2-30

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

Generating PCI Memory and I/O Cycles

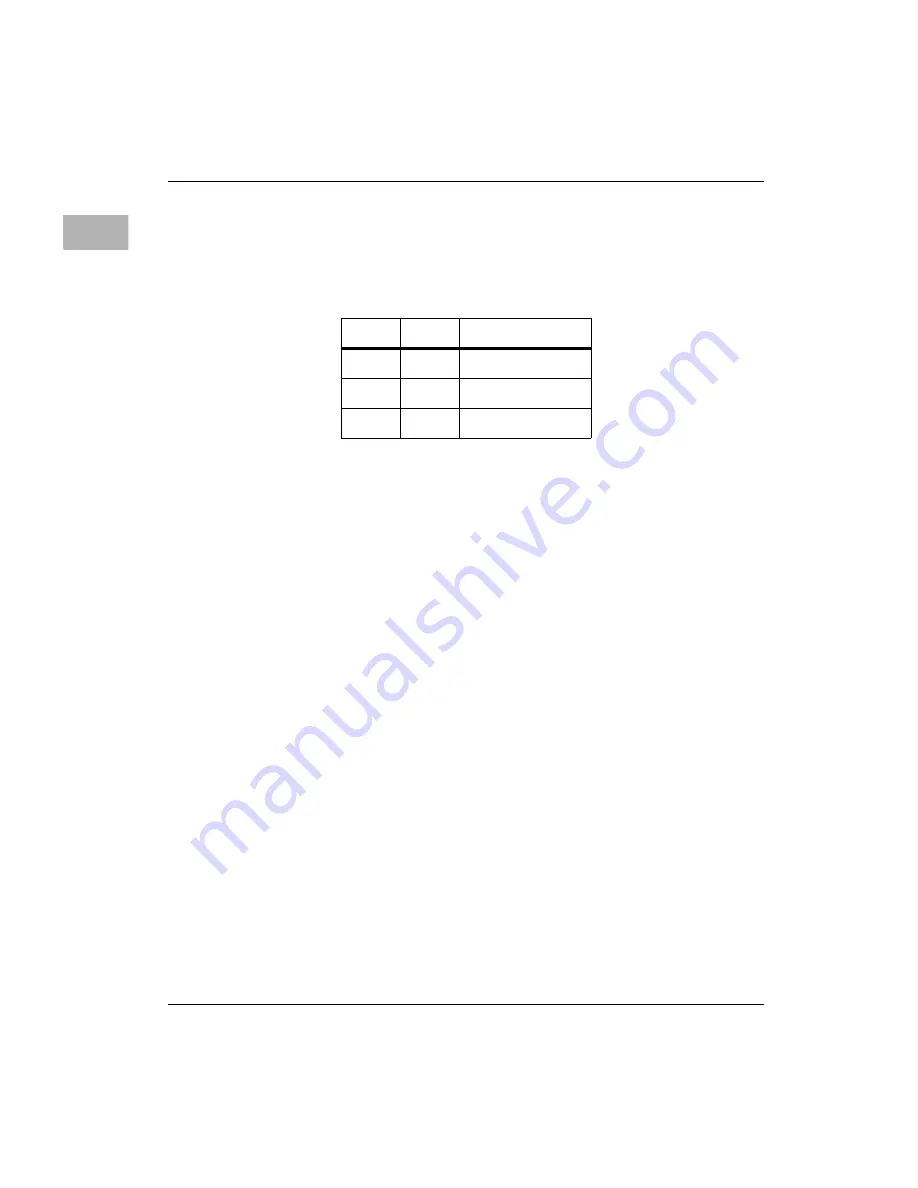

Each programmable slave may be configured to generate PCI I/O or

memory accesses through the MEM and IOM fields in its XSATTx

register as shown below.

:

If the MEM bit is set, the PHB performs Memory addressing on the PCI

bus. The PHB takes the PPC bus address, applies the offset specified in the

XSOFFx register, and maps the result directly to the PCI bus.

The IBM CHRP specification describes two approaches for handling PCI

I/O addressing: contiguous or spread address modes. When the MEM bit

is cleared, the IOM bit is used to select between these two modes whenever

a PCI I/O cycle is to be performed.

The PHB performs contiguous I/O addressing when the MEM bit is clear

and the IOM bit is clear. The PHB takes the PPC address, apply the offset

specified in the XSOFFx register, and map the result directly to PCI.

The PHB performs spread I/O addressing when the MEM bit is clear and

the IOM bit is set. The PHB takes the PPC address, applies the offset

specified in the MSOFFx register, and maps the result to PCI as shown in

MEM

IOM

PCI Cycle Type

1

x

Memory

0

0

Contiguous I/O

0

1

Spread I/O

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...