2-40

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

Address modification happens to the originating address regardless of

whether the transaction originates from the PCI bus or the PPC bus. The

three low order address bits are exclusive-ORed with a three-bit value that

depends on the length of the operand, as shown in

Note

The only legal data lengths supported in Little-Endian mode

are 1, 2, 4, or 8-byte aligned transfers.

Since this method has some difficulties dealing with unaligned PCI-

originated transfers, the PPC master of the PHB will break up all unaligned

PCI transfers into multiple aligned transfers into multiple aligned transfers

on the PPC bus.

PHB Registers

The PHB registers are not sensitive to changes in Big-Endian and Little-

Endian mode. With respect to the PPC bus (but not always the address

internal to the processor), the PPC registers are always represented in Big-

Endian mode. This means that the processor’s internal view of the PPC

registers appears different depending on which mode the processor

operates.

With respect to the PCI bus, the configuration registers are always

represented in Little-Endian mode.

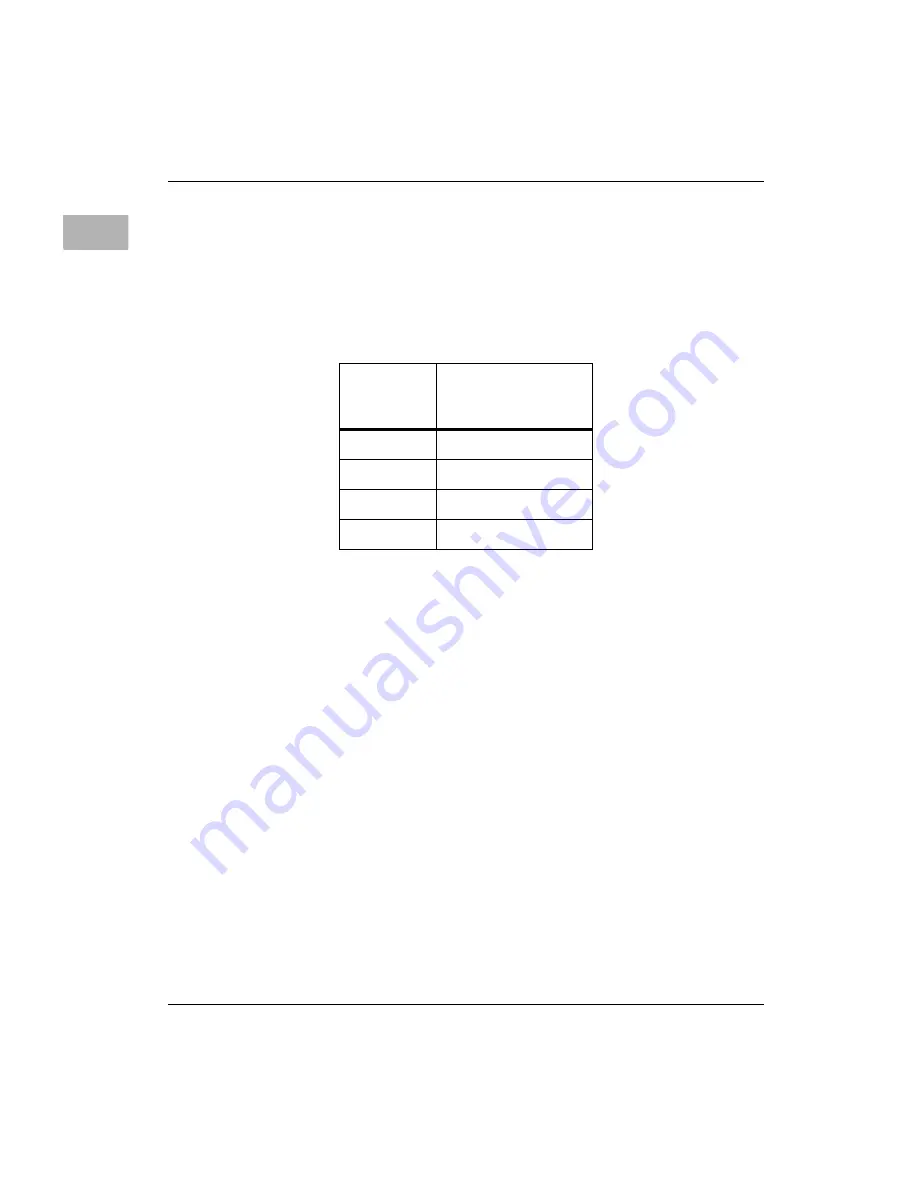

Table 2-13. Address Modification for Little Endian Transfers

Data

Length

(bytes)

Address

Modification

1

XOR with 111

2

XOR with 110

4

XOR with 100

8

no change

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...