Registers

http://www.motorola.com/computer/literature

2-101

2

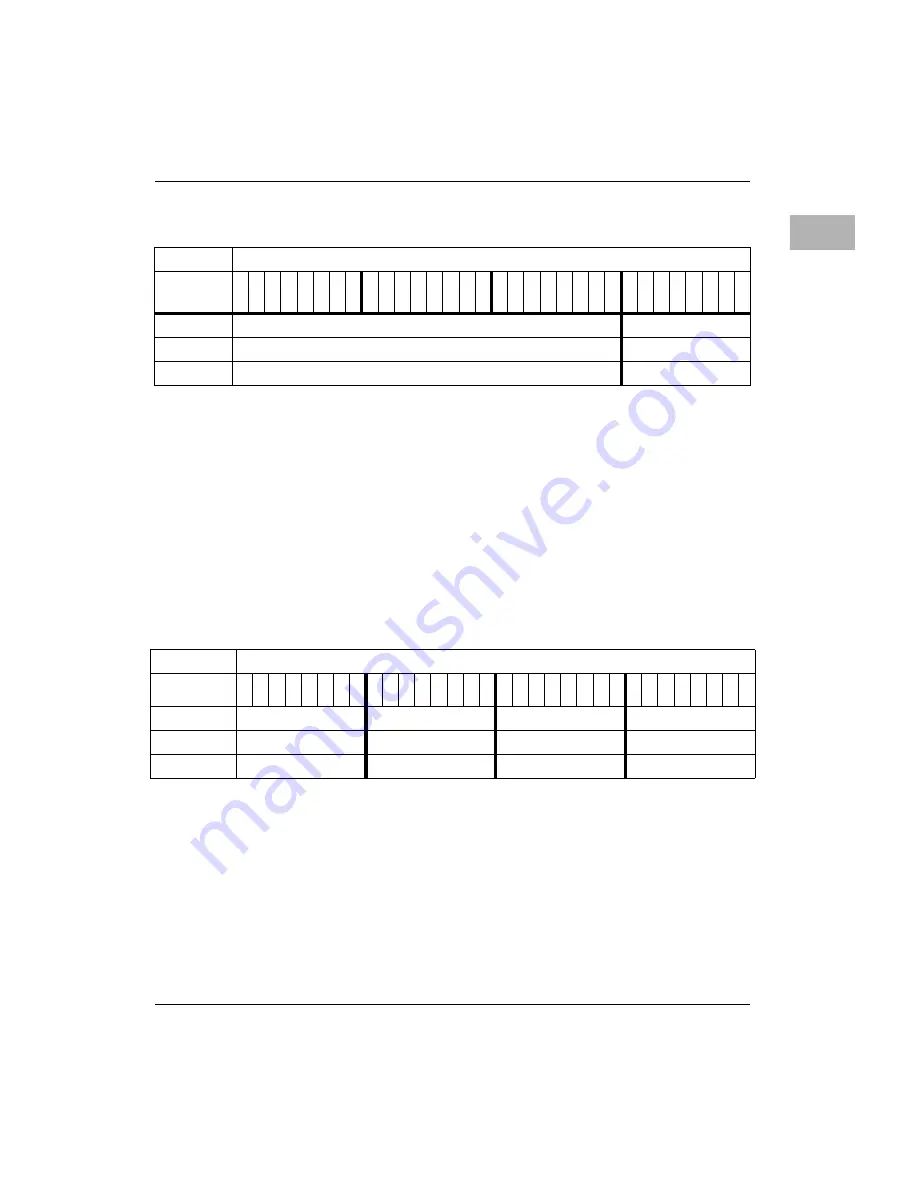

Revision ID/ Class Code Registers

REVID

Revision ID. This register identifies the PHB revision

level. This register is duplicated in the PPC Registers.

CLASS

Class Code. This register identifies PHB as the following:

Base Class Code

$06

PCI Bridge Device

Subclass Code

$00

PCI Host Bridge

Program Class Code

$00

Not Used

Header Type Register

The Header Type Register (Header) identifies the PHB as the following:

Header Type: $00 - Single Function Configuration Header

Offset

$08

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

CLASS

REVID

Operation

R

R

Reset

$060000

$01

Offset

$0C

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

HEADER

Operation

R

R

R

R

Reset

$00

$00

$00

$00

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...