3-2

Computer Group Literature Center Web Site

System Memory Controller (SMC)

3

❏

ROM/Flash Interface

– Two blocks with each block being 16 or 64 bits wide.

– Programmable access time on a per-block basis.

❏

I

2

C master interface.

❏

External status/control register support

Block Diagrams

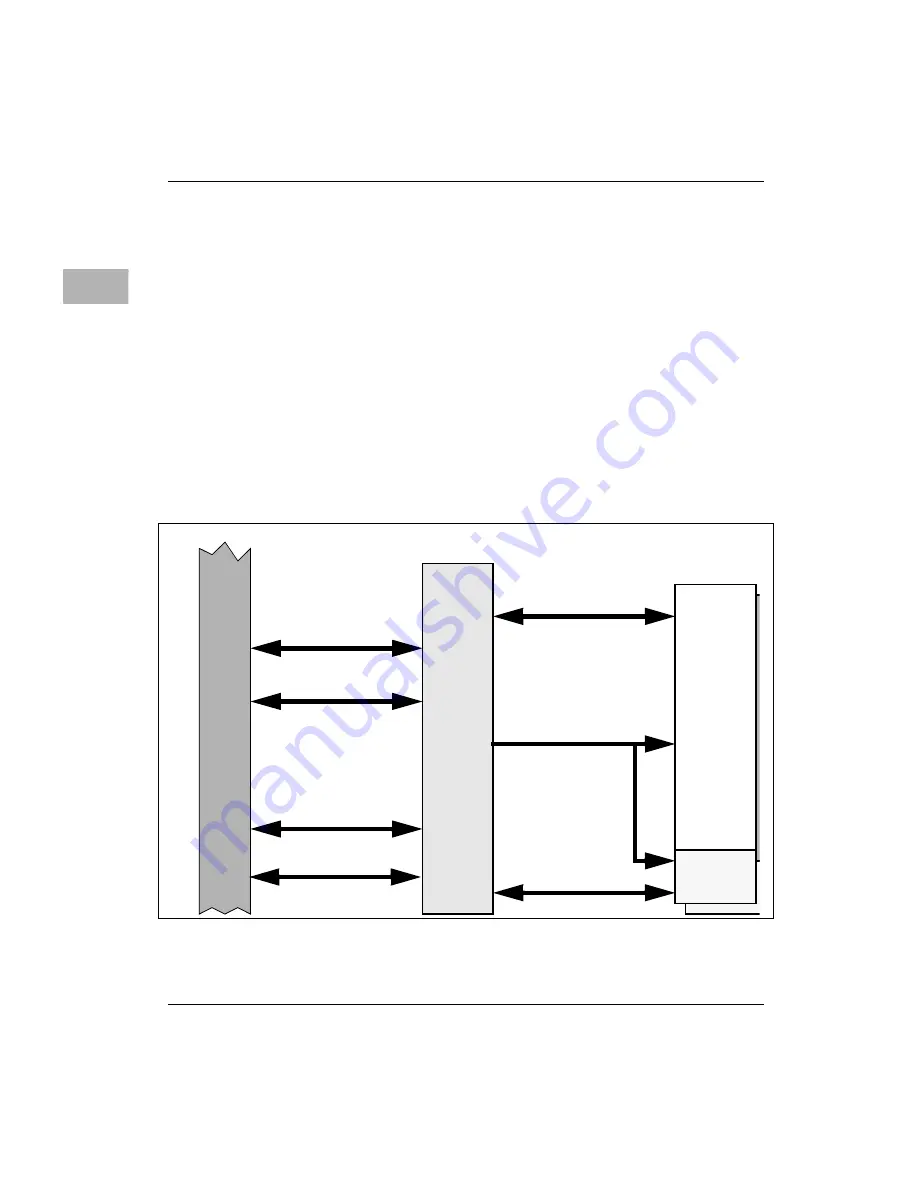

depicts a Hawk as it would be connected with SDRAMs in a

system.

shows the SMC’s internal data paths.

the overall SDRAM connections.

shows a block diagram of the

SMC portion of the Hawk ASIC.

Figure 3-1. Hawk Used with Synchronous DRAM in a System

PP

C60x Bus

DRAM

Synch

HAWK

Check

Data

PowerPC

Data (64 Bits)

PowerPC

SDRAM

Data (64 Bits)

SDRAM

Address & Control

SDRAM

Check Bits (8 Bits)

Address &Control

PowerPC

Data Parity (8 Bits)

PowerPC

Address Parity (4 bits)

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...