3-72

Computer Group Literature Center Web Site

System Memory Controller (SMC)

3

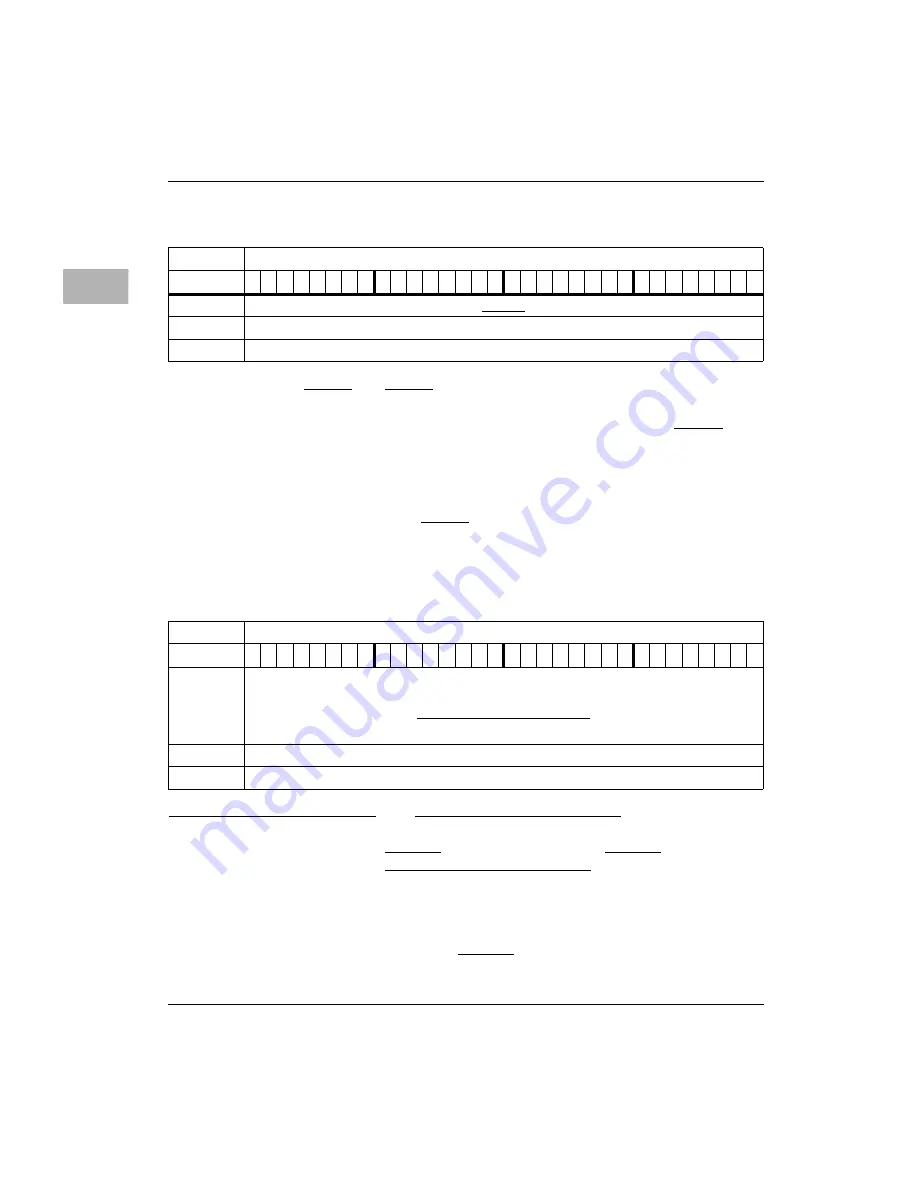

32-Bit Counter

CTR32

CTR32 is a 32-bit, free-running counter that increments

once per microsecond if the CLK_FREQUENCY register

has been programmed properly. Notice that CTR32 is

cleared by power-up and local reset.

Note

When the system clock is a fractional frequency, such as

66.67 MHz, CTR32 will count at a fractional amount faster or

slower than 1 MHz, depending on the programming of the

CLK_FREQUENCY Register.

External Register Set

EXTERNAL REGISTER SET The EXTERNAL REGISTER SET is user provided and

is external to the Hawk. It is enabled only when the

tben_en bit is cleared. When the tben_en bit is set, the

EXTERNAL REGISTER SET is disabled and the Hawk

does not respond in its range except for the tben register at

$FEF88300.

The tben register (which is internal to Hawk) responds

only when tben_en is set.

Address

$FEF80100

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

CTR32

Operation

READ/WRITE

Reset

0 PL

Address

$FEF88000 - $FEF8FFF8

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

EXTERNAL REGISTER SET

Operation

READ/WRITE

Reset

X PL

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...