B-10

Computer Group Literature Center Web Site

MVME5100 VPD Reference Information

B

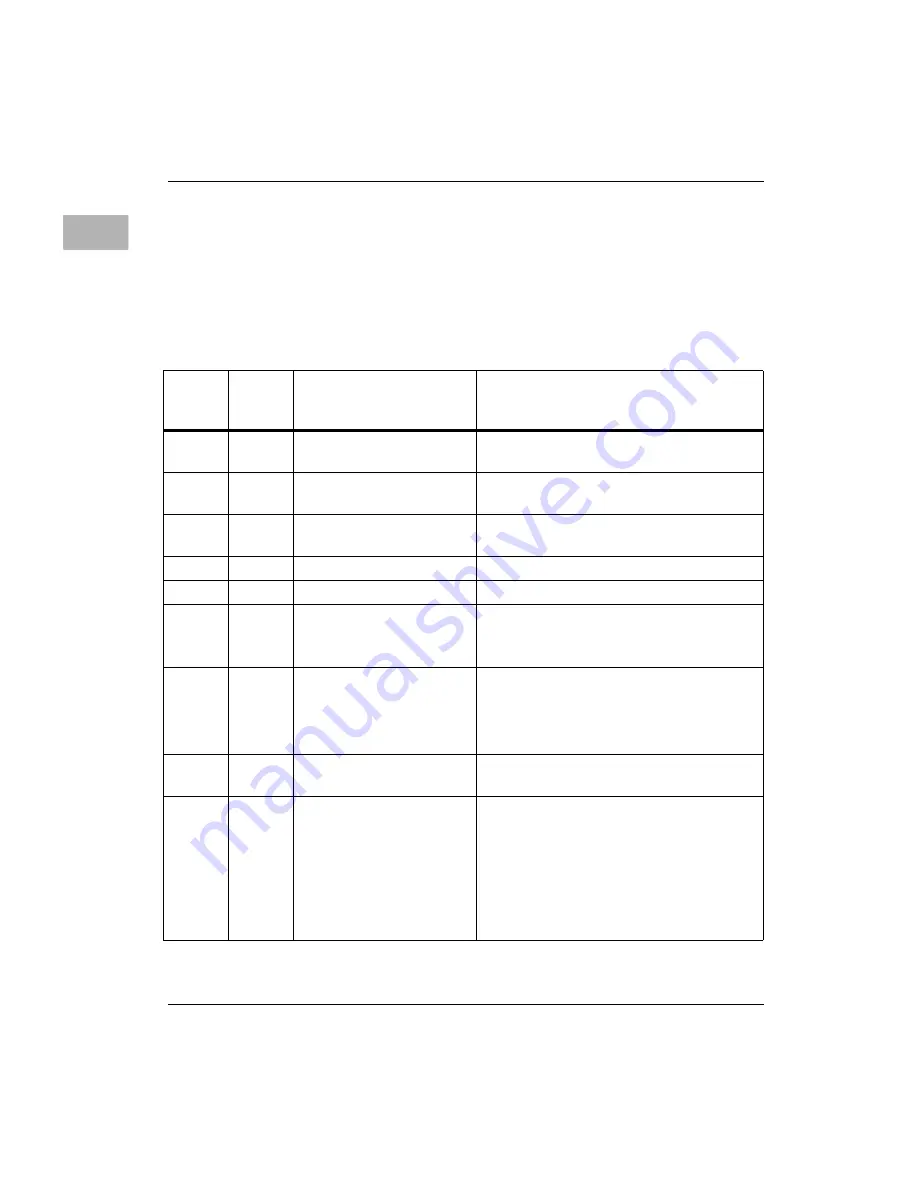

VPD Definitions - L2 Cache Configuration Data

The L2 cache configuration data packet consists of byte fields that show

the size, organization, and type of the L2 cache memory array. Note: The

PPMCBASE does not contain L2 Cache . The following table(s) further

describe the L2 cache memory configuration VPD data packet.

Table B-4. L2 Cache Configuration Data

Byte

Offset

Field

Size

(Bytes)

Field Mnemonic

Field Description

00

2

L2C_MID

Manufacturer’s Identifier (FFFF =

Undefined/Not-Applicable)

02

2

L2C_DID

Manufacturer’s Device Identifier (FFFF =

Undefined/Not-Applicable)

04

1

L2C_DDW

Device Data Width (e.g., 8-bits, 16-bits, 32-

bits, 64-bits, 128-bits)

05

1

L2C_NOD

Number of Devices Present

06

1

L2C_NOC

Number of Columns (Interleaves)

07

1

L2C_CW

Column Width in Bits

This will always be a multiple of the device’s

data width.

08

1

L2C_TYPE

L2 Cache Type:

00 - Arthur Backside

01 - External

02 - In-Line

09

1

L2C_ASSOCIATE

Associative Microprocessor Number (If

Applicable)

0A

1

L2C_OPERATIONMODE

Operation Mode:

00 - Either Write-Through or Write-Back

(S/W Configurable)

01 - Either Write-Through or Write-Back

(H/W Configurable)

02 - Write-Through Only

03 - Write-Back Only

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...