Memory maps

http://www.motorola.com/computer/literature

1-5

1

Note

The first 1MB of ROM/FLASH Bank A (soldered Flash up

to 8MB) appears in this range after a reset if the rom_b_rv

control bit in the SMC’s ROM B Base/Size register is

cleared. If the rom_b_rv control bit is set, this address range

maps to ROM/FLASH Bank B (socketed 1MB Flash).

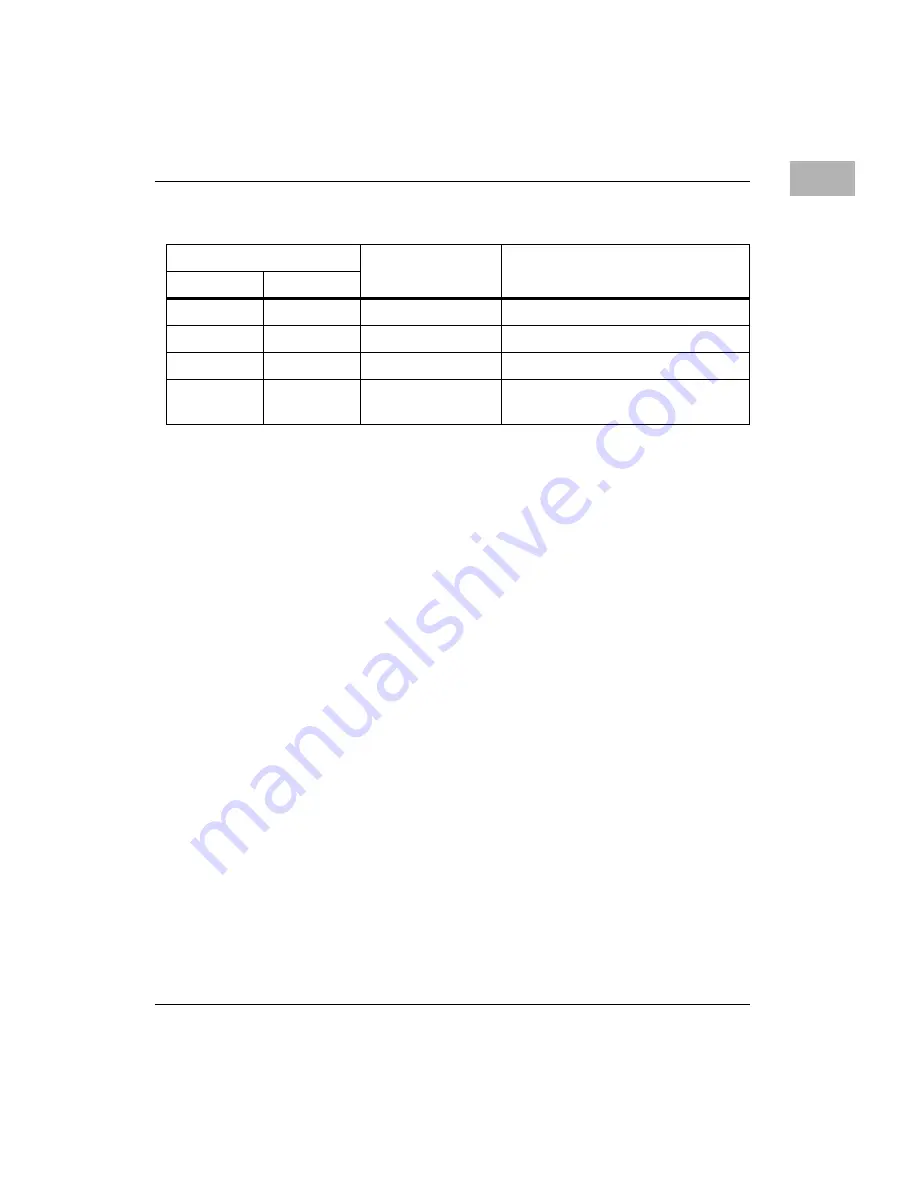

For an example of the CHRP memory map refer to the following table. For

detailed processor memory maps, including suggested CHRP- and PREP-

compatible memory maps, refer to the Hawk related portion of this

manual.

Processor Memory Map

The following table describes a suggested CHRP Memory Map from the

point of view of the processor. This memory map is an alternative to the

PREP memory map. Note: in all recommended CHRP maps, the beginning

of PCI Memory Space is determined by the end of DRAM rounded up to

the nearest 256MB-boundry as required by CHRP. For example, if

memory was 1G on the baseboard and 192MB on a mezzanine, the

beginning of PCI memory would be rounded up to address 0x50000000

(1G + 256M).

FEF9 0000

FEFE FFFF

384KB

Not Mapped

FEFF 0000

FEFF FFFF

64KB

PCI Host Bridge (PHB) Registers

FF00 0000

FFEF FFFF

15MB

Not Mapped

FFF0 0000

FFFF FFFF

1MB

ROM/FLASH Bank A or Bank B (See

Note)

Table 1-2. Default Processor Memory Map (Continued)

Processor Address

Size

Definition

Start

End

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...