Memory maps

http://www.motorola.com/computer/literature

1-7

1

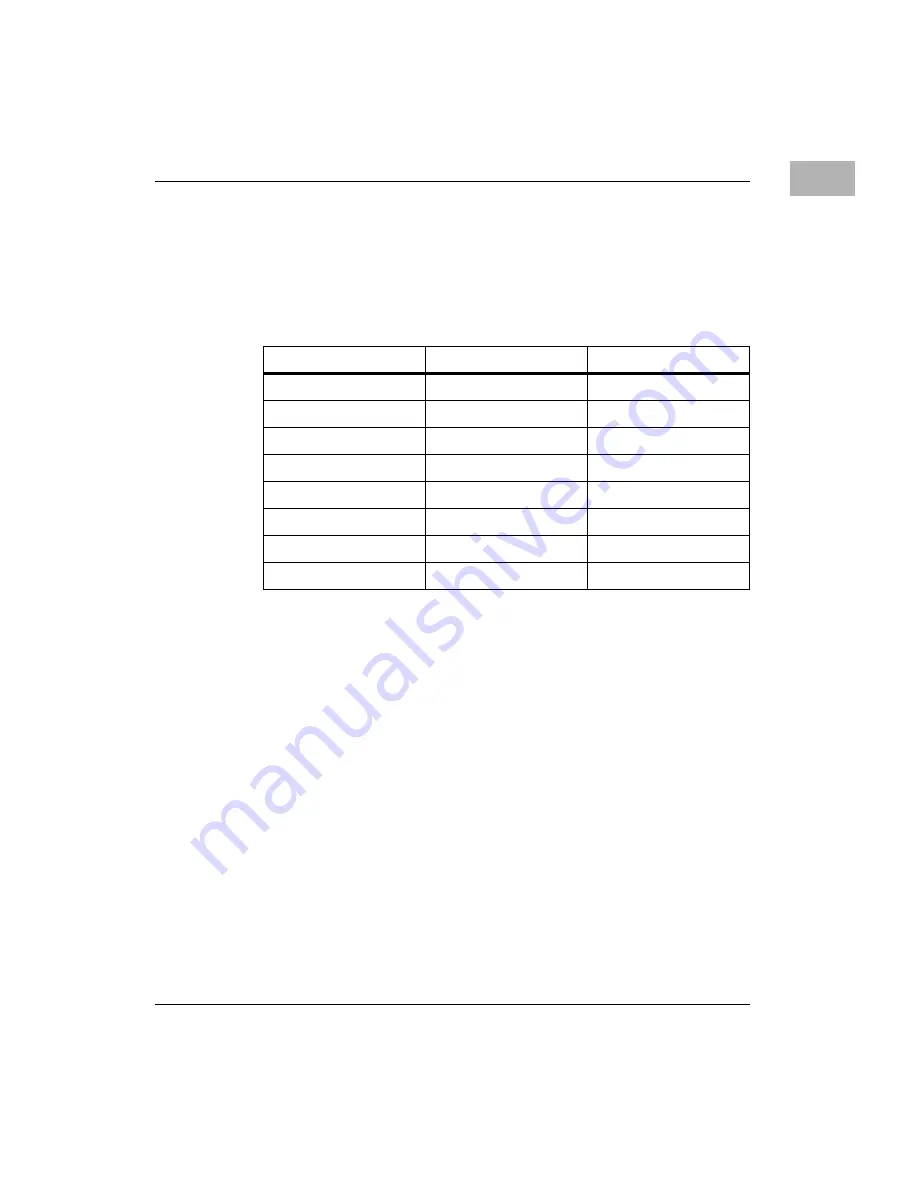

The following table shows the programmed values for the associated

Hawk PCI Host Bridge Registers for the suggested Processor Memory

Map.

PCI Memory Map

Following a reset, the Hawk ASIC disable’s all PCI slave map decoders.

The MVME5100 is fully capable of supporting both PREP and CHRP PCI

Memory Maps with RAM size limited to 2GB. The default values for the

PCI Slave Image registers, are listed in Chapter 3, PPCBug, of the

MVME5100 Single Board Computer Installation and Use manual.

VME Memory Map

The MVME5100 is fully capable of supporting both the PREP and the

CHRP VME Memory Maps with RAM size limited to 2GB. The default

values for the VME Slave Image registers are listed in Chapter 3, PPCBug,

of the MVME5100 Single Board Computer Installation and Use manual.

Table 1-4. Hawk PPC Register Values for Suggested Memory

Map

Address

Register Name

Register Name

FEFF 0040

MSADD0

X000 F3FF [X:1..8]

FEFF 0044

MSOFF0 & MSATT0

0000 00C2

FEFF 0048

MSADD1

FE00 FE7F

FEFF 004C

MSOFF1 & MSATT1

0200 00C0

FEFF 0050

MSADD2

0000 0000

FEFF 0054

MSOFF2 & MSATT2

0000 0000

FEFF 0058

MSADD3

0000 0000

FEFF 005C

MSOFF3 & MSATT3

0000 0000

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...