PCI Local Bus

http://www.motorola.com/computer/literature

1-23

1

Dual TL16C550 UARTs

The MVME5100 implementation of the Dual TL16C550 UARTs are fully

compliant with the PowerPlus II Programming Model for UART

Registers. The following tables reflect this model.

The MVME5100 uses UART-1 and UART-2 for asynchronous serial

debug ports (four are allowed by the PowerPlus II Programming Model).

The first UART (UART-1) is addressed at External Register Set Address

Offset $8000 (FEF8 8000). The second (UART-2) is addressed at offset

$8200 (FEF8 8200). The UART 8-bit data port (RD0-RD7) is connected

to the most significant bits of the 64-bit External Register Set. The UART

port addressing occurs on 16-byte address boundaries, and are backward

compatible with the PPMC750.

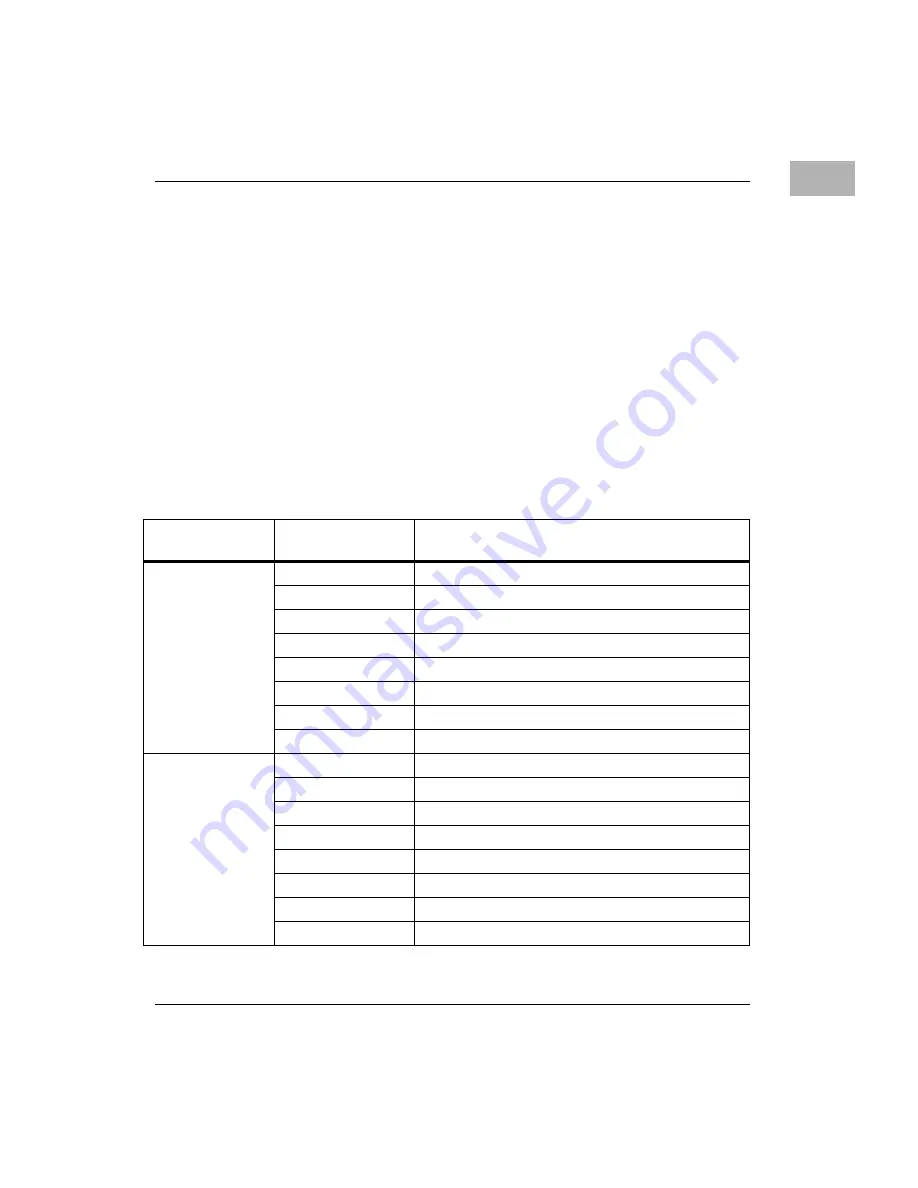

Table 1-10. 16550 Access Registers

Required or

Optional

External Register

Set Address Offset

Function

UART-1 Registers

8000

Receiver Buffer (Read), Transmitter Holding (Write)

8010

Interrupt Enable

8020

Interrupt Identification (Read), FIFO Control (Write)

8030

Line Control

8040

MODEM Control

8050

Line Status

8060

MODEM Status

8070

Scratch

UART-2 Registers

8200

Receiver Buffer (Read), Transmitter Holding (Write)

8210

Interrupt Enable

8220

Interrupt Identification (Read), FIFI Control (Write)

8230

Line Control

8240

MODEM Control

8250

Line Status

8260

MODEM Status

8270

Scratch

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...