2-36

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

When the arbiter is programmed for round robin priority mode, the arbiter

maintains fairness and provides equal opportunity to the requestors by

rotating its grants. The contents in “HEIR” field are “don’t cares” when

operated in this mode.

When the arbiter is programmed for mixed mode, the 8 requestors are

divided up into 4 groups and each groups is occupied by 2 requestors.

PARB6 and PARB5 are defined in group1; PARB4 and PARB3 are

defined in group 2; PARB2 and PARB1 are defined in group 3; PARB0

and HAWK are defined in group 4. Arbitration is set for round robin mode

between the 2 requestors within each group and set for fixed mode between

the 4 groups. The levels of priority for each group are programmable by

writing the “HEIR” field in the PCI Arbiter control register.

describes all available setting for the “HEIR” field in mixed mode.

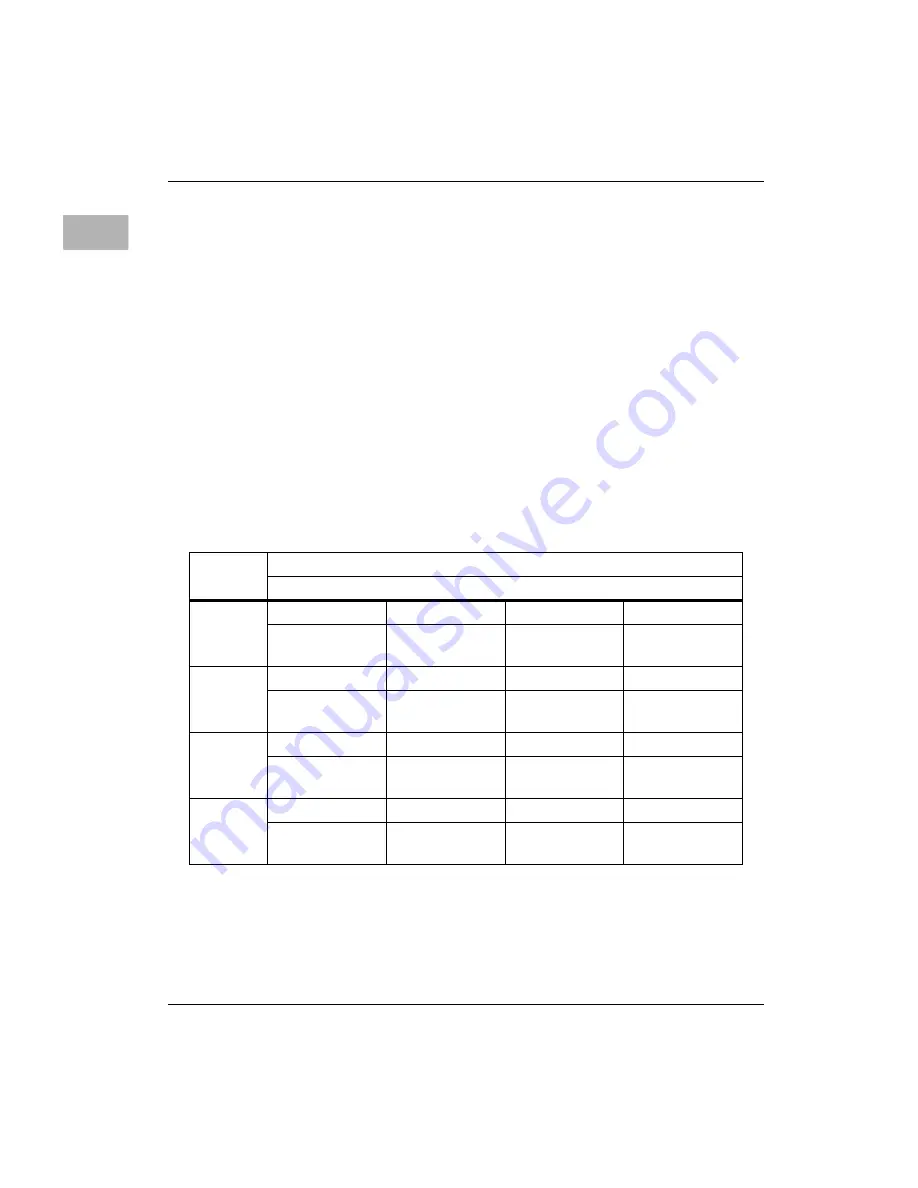

Table 2-11. Mixed Mode Priority Level Setting

HEIR

Setting

PRIORITY Levels

Highest

Lowest

000

group 1

group 2

group 3

group 4

PARB6 & 5

PARB4 & 3

PARB2 & 1

PARB0 &

HAWK

001

group 4

group 1

group 2

group 3

PARB0 &

HAWK

PARB6 & 5

PARB4 & 3

PARB2 & 1

010

group 3

group 4

group 1

group 2

PARB2 & 1

PARB0 &

HAWK

PARB6 & 5

PARB4 & 3

011

group 2

group 3

group 4

group 1

PARB4 & 3

PARB2 & 1

PARB0 &

HAWK

PARB6 & 5

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...