603 Hardware Specifications

13

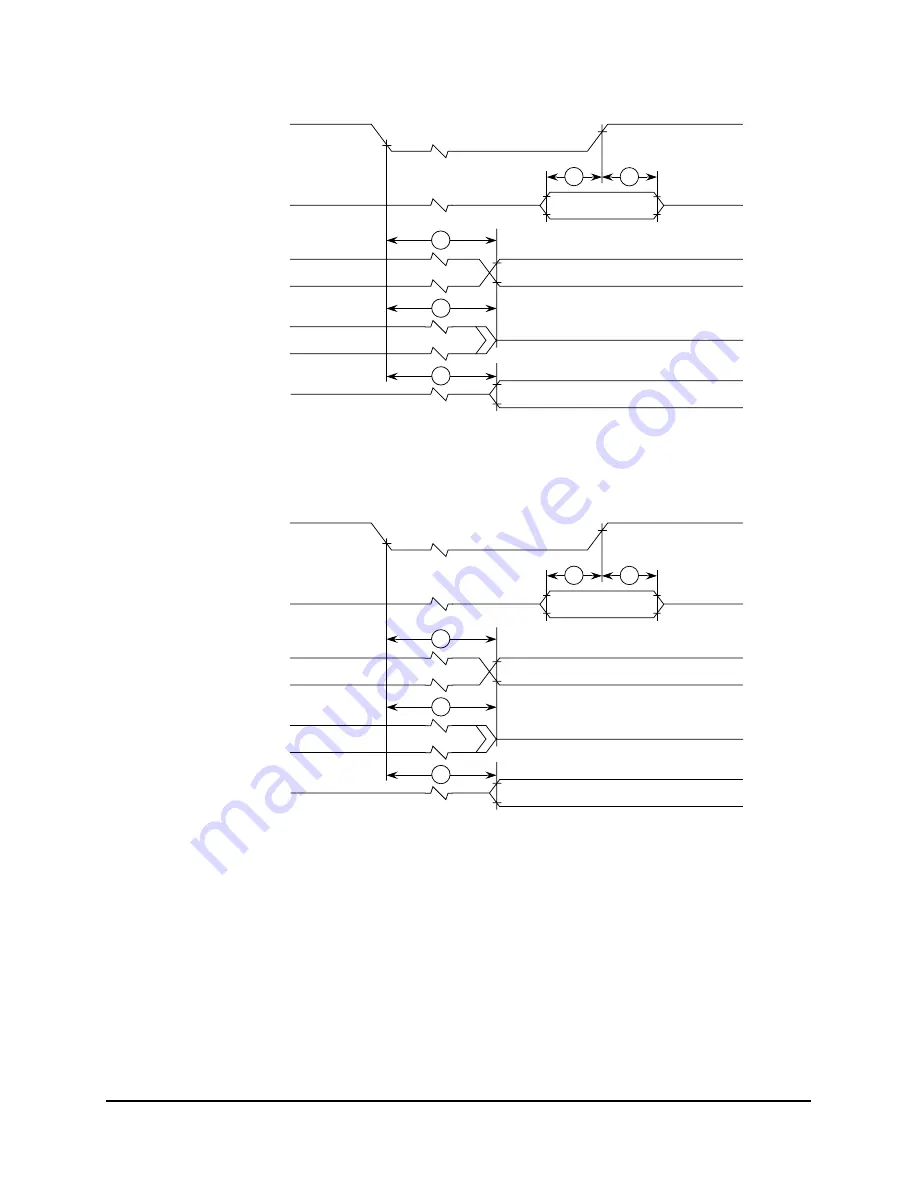

Figure 7 provides the boundary-scan timing diagram.

Figure 7. Boundary-Scan Timing Diagram

Figure 8 provides the test access port timing diagram.

Figure 8. Test Access Port Timing Diagram

6

7

Input Data Valid

8

9

8

Output Data Valid

Output Data Valid

TCK

Data Inputs

Data Outputs

Data Outputs

Data Outputs

VM

VM

10

11

Input Data Valid

12

13

12

Output Data Valid

Output Data Valid

TCK

TDI, TMS

TDO

TDO

TDO

VM

VM