22

603 Hardware Specifications

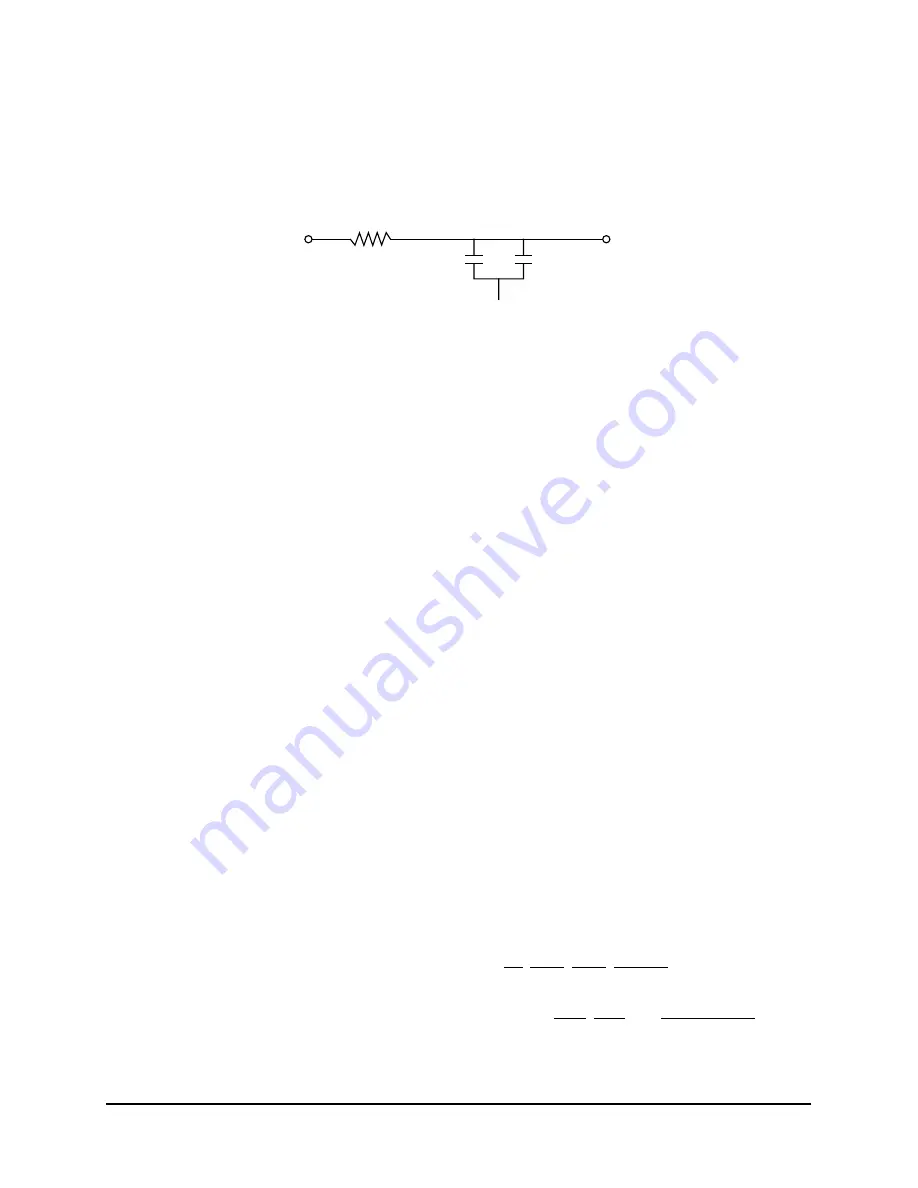

1.8.2 PLL Power Supply Filtering

The AVdd power signal is provided on the 603 to provide power to the clock generation phased-lock loop.

To ensure stability of the internal clock, the power supplied to the AVdd input signal should be filtered using

a circuit similar to the one shown in Figure 12. The circuit should be placed as close as possible to the AVdd

signal to ensure it filters out as much noise as possible.

Figure 12. PLL Power Supply Filter Circuit

1.8.3 Decoupling Recommendations

Due to the 603’s dynamic power management feature, large address and data buses, and high operating

frequencies, the 603 can generate transient power surges and high frequency noise in its power supply,

especially while driving large capacitive loads. This noise must be prevented from reaching other

components in the 603 system, and the 603 itself requires a clean, tightly regulated source of power.

Therefore, it is recommended that the system designer place at least one decoupling capacitor at each Vdd

and OVdd pin of the 603. It is also recommended that these decoupling capacitors receive their power from

separate Vdd, OVdd, and GND power planes in the PCB, utilizing short traces to minimize inductance.

These capacitors should vary in value from 220 pF to 10

µ

F to provide both high- and low-frequency

filtering, and should be placed as close as possible to their associated Vdd or OVdd pin. Suggested values

for the Vdd pins—220 pF (ceramic), 0.01

µ

F (ceramic), and 0.1

µ

F (ceramic). Suggested values for the

OVdd pins—0.01

µ

F (ceramic), 0.1

µ

F (ceramic), and 10

µ

F (tantalum). Only SMT (surface mount

technology) capacitors should be used to minimize lead inductance.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB,

feeding the Vdd and OVdd planes, to enable quick recharging of the smaller chip capacitors. These bulk

capacitors should also have a low ESR (equivalent series resistance) rating to ensure the quick response time

necessary. They should also be connected to the power and ground planes through two vias to minimize

inductance. Suggested bulk capacitors—100

µ

F (AVX TPS tantalum) or 330

µ

F (AVX TPS tantalum).

1.8.4 Connection Recommendations

To ensure reliable operation, it is recommended to connect unused inputs to an appropriate signal level.

Unused active low inputs should be connected to Vdd. Unused active high inputs should be connected to

GND.

1.8.5 Pull-up Resistor Requirements

The 603 requires high-resistive (weak: 10 K

Ω

) pull-up resistors on several control signals of the bus

interface to maintain the control signals in the negated state after they have been actively negated and

released by the 603 or other bus master. These signals are—TS, ABB, DBB, ARTRY.

In addition, the 603 has three open-drain style outputs that require pull-up resistors (weak or stronger:

4.7 K

Ω

–10 K

Ω

) if they are used by the system. These signals are—APE, DPE, and CKSTP_OUT.

During inactive periods on the bus, the address and transfer attributes on the bus are not driven by any master

Vdd

AVdd

10

Ω

10

µ

F

0

.

1

µ

F

GND