5-2

SE4400 Integration Guide

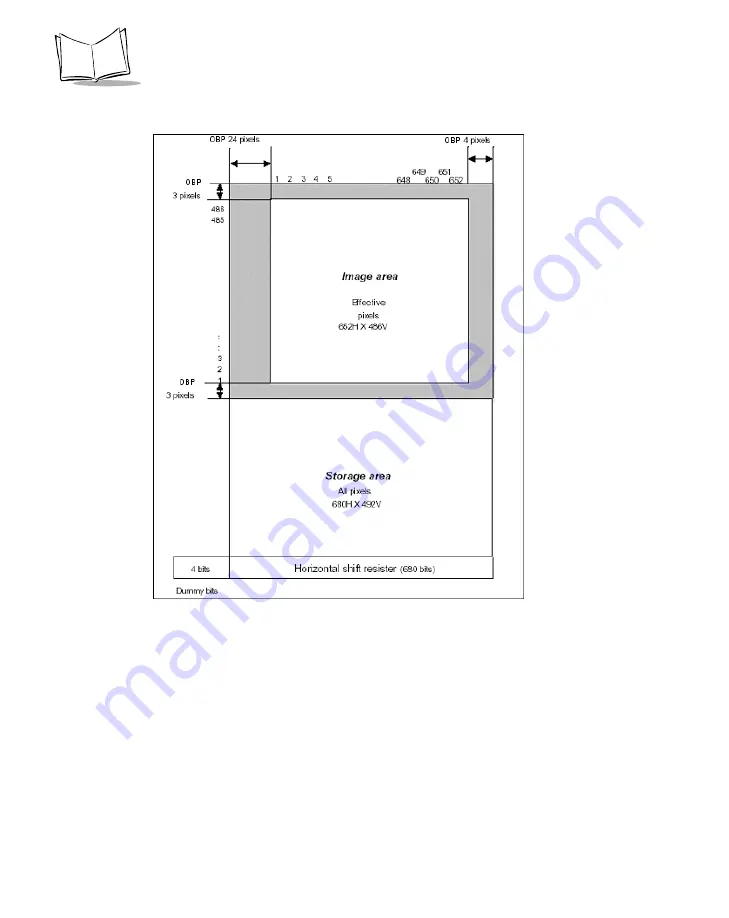

Figure 5-1. Pixel Layout

To operate properly, the CCD chipset requires a clock near 24 MHz. To achieve this, an

internal PLL multiplies the incoming 12 MHz MCKI by two to generate the 24 MHz internal

camera clock, MCK. (If using a 6 MHz MCKI, refer to the

LC99704B-WK3 Sanyo DSP

Specification

, Version 1). During pixel array read-out, the camera converts a pixel to an 8-

bit digital value at a rate of one half of MCK; therefore the pixel clock, PCLK, is generated

at a frequency of 12 MHz.

*OBP = Optically Blocked Pixels, which are not photosensitive.

Summary of Contents for Symbol SE4400

Page 1: ...SE4400 Integration Guide ...

Page 2: ......

Page 3: ...SE4400 Integration Guide 72E 63399 04 Revision A January 2007 ...

Page 6: ...iv ...

Page 9: ...vii Contents Index Feedback ...

Page 10: ...viii SE4400 Integration Guide ...

Page 48: ...3 22 SE4400 Integration Guide ...

Page 78: ...5 20 SE4400 Integration Guide ...

Page 90: ...Index 4 SE4400 Integration Guide ...

Page 92: ......

Page 93: ......