3-

61

3-

62

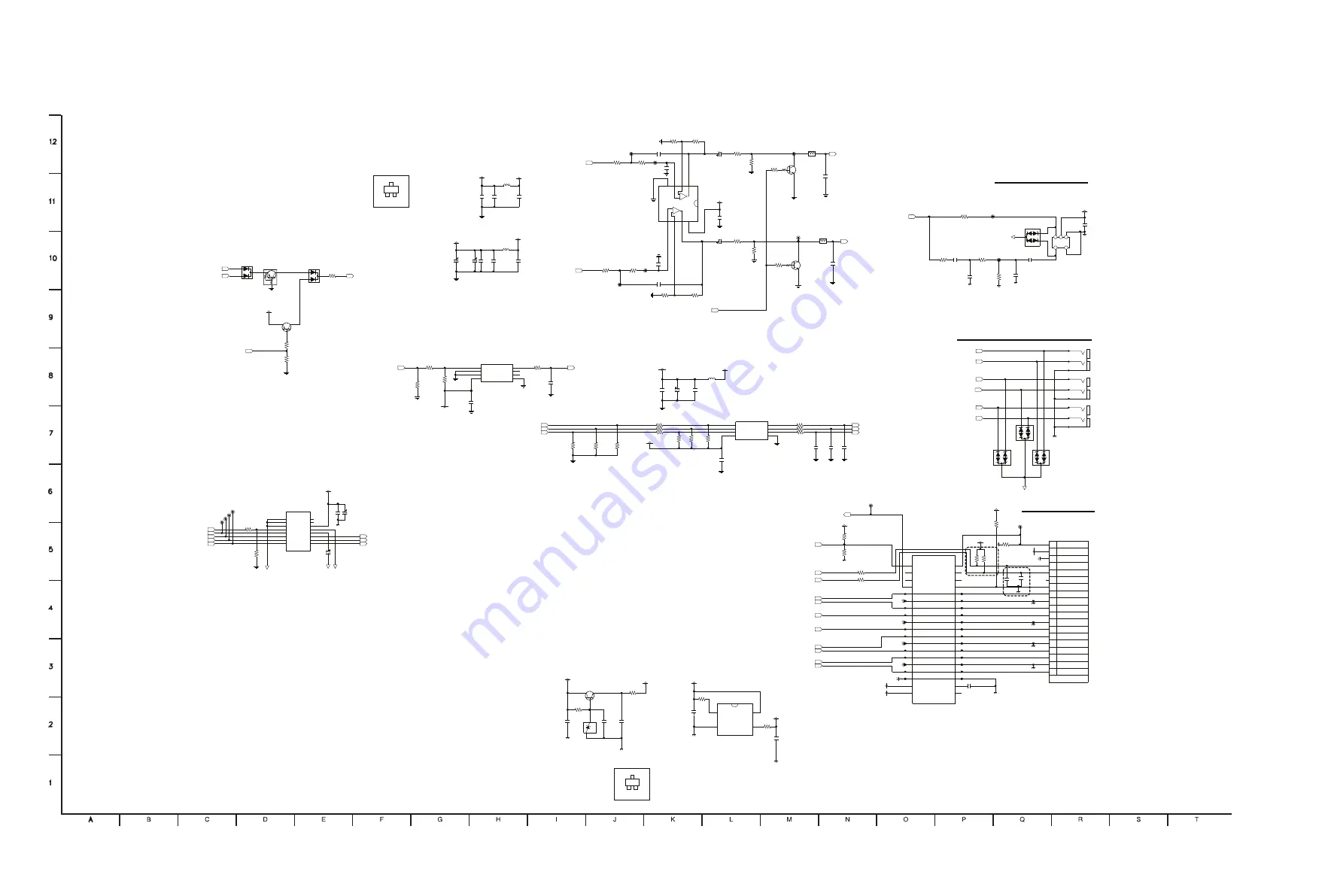

6. A/V OUTPUT CIRCUIT DIAGRAM

7V

7V

12V

12V

7V

7V

12V

12V

7V

7V

12V

12V

7V

7V

12V

12V

A

-

B

+

+

-

CVBS

F4

HDMI_2_P

5:C5

HDMI_0_P

5:C5

COMP_Pr

I5

TP611

HDMI_1_N

5:C5

DGND

DGND

COMP_Y

I5

VCC_5V_AV

HDMI_1_P

5:C5

HDMI_2_N

5:C5

TP619

HDMI_SCL

5:C5

HDMI_HTPLG

5:C5

TP622

DGND

VCC_5V_AV

AUDIO_FRONTR

I1

AUDIO_FRONTL

I2

DGND

HDMI_SDA

5:C5

AUD0_SPDIF

5:F5;5:H6

HDMI_0_N

5:C5

VCC_5V_AV

HDMI_CLK_N

5:C5

COMP_Pb

I5

HDMI_CLK_P

5:C5

VCC_12V_AUDIO

VCC_12V_AMP

DGND

DGND

VCC_5V_AUDIO

I2S_S_DATA

5:F5;5:H6

I2S_S_CLK

5:F5

I2S_S_LR

5:F5

AOUT_R

F1

AOUT_L

F3

R672

4.3K(5%)

R675

4.3K(5%)

TP628

DGND

AOUT_L

C6

L618

10uH_2012

TP629

R636

33K(1%)

R639

33K(1%)

TP630

AUDIO_MUTE

C3

DGND

AOUT_R

C6

L619

10uH_2012

TP631

DGND

TP632

DGND

TP633

AUDIO_FRONTR

J4

AUDIO_MUTE_DAC

B3

AUD_FS_CLK0

4:B7;5:F5

D604

PG712FBS23

DGND

DGND

DGNDDGND

JK602

1

2

3

4

5

6

7

8

9

IC607

PCM1781

FMT

1

DEMP0

2

DEMP1

3

MUTE

4

SCK

5

DATA

6

BCK

7

LRCK

8

TEST

9

NC

10

VCC

11

AGND

12

VCOM

13

VO_R

14

VO_L

15

ZEROA

16

DGND

VCC_12V_AMP

DGND

CA614

100UF/16V

CA624

100UF/16V

IC609

IP4776CZ38

26

NC

1

VCC(5.3V)

11

TMDS_GND

35

NC

3

GND

8

TMDS_GND

6

NC

34

TMDS_GND

27

TMDS_D0-

33

TMDS_D2-

7

5

TMDS_GND

30

TMDS_D1-

9

NC

28

TMDS_GND

10

29

NC

4

31

TMDS_GND

36

GND

2

VCC(3.3V)

32

NC

12

NC

25

TMDS_GND

13

T

14

TMDS_GND

23

CEC_OUT

24

TMDS_CLK-

15

NC

22

DDC_CLK_OUT

16

CEC_IN

21

DDC_DAT_OUT

17

DDC_CLK_IN

18

DDC_DAT_IN

19

HOT_PLUG_DET_IN

20

HOT_PLUG_DET_OUT

37

TMDS_BIAS

38

NC

TP635

TP636

TP637

TP638

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

VCC_3.3V_L

DGND

VCC_5.6V_L

VCC_3.3V_L

HDMI_CEC_CON

4:K4

CA630

100UF/16V

CA631

100UF/16V

DGND

VCC_5V_AUDIO

VCC_5V_AV

DGND

R6D3

10K(1%)

R6D4

20K(1%)

DGND

CA634

22uF/16V

DGND

R6D5

10K(1%)

R6D6

20K(1%)

DGND

CA635

22uF/16V

DGND

VCC_5.6V_L

VCC_3.3V_L

IC708

XC6221B332NR_open

1

CE

2

VSS

3

VOUT

4

VIN

DGND

DGND

DGND

JK601

1

2

3

A

B

TP641

C675

0.1uF

C627

0.1uF

C671

0.1uF

C621

0.1uF

C676

0.1uF

C683

0.1uF

C634

0.1uF

C639

0.1uF

R6D2

27k

R6C9

15k

AUDIO_FRONTL J4

DGND

D605

PG712FBS23

JK603

1

TX2+

2

TX2_SHD

3

TX2

4

TX1+

5

TX1_SHD

6

TX1

7

TX0+

8

TX0_SHD

9

TX0

10

11

TXC_SHD

12

TX_CLK

13

CEC

14

NC

15

SCL

16

SDA

17

GND

18

VCC +5V

19

HPD

L616

4.7UH

L621

4.7UH

R663

120

R642

120

C651

470pF

C612

470pF

R6F1

130

R6E9

120

C690

0.47uF

C689

0.47uF

C687

100pF

C688

100pF

C672

0.1uF

C684

OPEN

C674

1uF_open

C673

1uF_open

R648

1.5k

R641

1.5k

R6D0

4.7k_open

R6F0

56

R6D7

100

R676

open

R635

OPEN

C685

open

C686

open

R673

open

R6D8

0

R6D9

0

D611

OPEN

D610

OPEN

C677

150pF

C678

150pF

VCC_3V3

R677

OPEN

AUD_MUTE/GPIO_06

5:F3

R681

OPEN

R682

0

DGND

R687

0

R688

0

Q614

KRC281S

E

C

B

Q615

KRC281S

E

C

B

DGND

AUDIO_MUTE_DAC

C6

MICOM_AUD_MUTE

4:D7;4:J4

AUDIO_MUTE

H3

C696

OPEN

DGND

DGND

C697

OPEN

D612

KDS121

C699

1uF

VCC_3.3V_L

VCC_5.6V_L

D613

BZX84-C3V6

C6A0

1uF

R6F7

110

C698

1uF

R6F9

0

R6F8

0_open

DGND

DGND

Q617

2SA1037K

B

E

C

R689

1k

R690

10k

DGND

VCC_5.6V_L

Q616

KTC3265Y

B

E

C

Q618

KRA103S-T1

E

C

B

DGND

IC603

NJM13404AV

1

2

3

4

5

6

7

8

DGND

C668

OPEN

DGND

IC606

THS7314

IN_CH1

1

IN_CH2

2

IN_CH3

3

VS+

4

GND

5

OUT_CH3

6

OUT_CH2

7

OUT_CH1

8

DGND

VDAC_Pr

5:B4

C681

OPEN

R6B2

OPEN

IC610

THS7316

1

1

IN_CH1

2

2

IN_CH2

3

3

IN_CH3

4

4

VS+

5

5

GND

6

6

OUT_CH3

7

7

OUT_CH2

8

8

OUT_CH1

VDAC_CVBS

5:B4

DGND

DGND

R637

75(1%)

R606

75(1%)

DGND

R6B4

OPEN

R650

75

VCC_3V3_VIDEO

VDAC_Pb

5:B4

R6B1

OPEN

C680

OPEN

C616

0.1uF

DGND

VDAC_Y

5:B4

R621

75(1%)

R651

75

VCC_3V3

C695

22uF

C667

0.1uF

CA628

470uF/6V

C679

OPEN

DGND

CVBS

J4

DGND

DGND

COMP_Pr

J4

COMP_Pb

J4

R632

75

COMP_Y

J3

VCC_3V3_VIDEO

C609

0.1uF

DGND

VCC_3V3_VIDEO

R652

75

R6B3

OPEN

R640

75(1%)

L614

4.7UH

DGND

R691

0

R692

0

R693

0

R694

0

D614

KDS121

AUD_MUTE/GPIO_06

5:F3

R6F6

0

OPTICAL/COAXIAL OUT

COMPONENT,CVBS ,2CH AUDIO

PG712FBS23

HDMI

1

At each differential pair

trace impedance must be

100 ohm.

2

3

2009.2.16

6. A/V Output

4.Route differential pairs above gnd plane and gnd plane are not split under differential pairs.

2.Match Trace length of differential pairs.

7.Trace Length must be less than 100mm.

3.Trace spacing is same as trace width within pair signals.

6.Trace spacing between DP/DN and other traces must be more than 5 times of DP/DN trace width.

5.Avoid via aspossible as you can.

1.HDMI differential pair signals must be routed as 100ohm differential pairs.

*HDMI Design & Layout Guide*

*Audio & Video Signal Layout Guide*

1.Component & CVBS signal traces must be routed using signal to signal spacing is more than 0.25mm.

C671 and CA627 must be placed near by PCM1781

Place IC609(ESD protection IC)

as close as possible to

HDMI connector.

Place R641,R648,C685 and C686 on the top of PCB

Maximum capacitance of DDC line is 50pF,

be short and remove GND plane around DDC

Maximum CEC line leakage current in off (unpowered) state : 1.8uA

2.2K

2.2K

22K

22K

1

KRC281S(SOT23)

C

B

2

3

E

Termination Resistor are placed close to Video Filter

Summary of Contents for M56

Page 14: ...MEMO 2 7...

Page 54: ...5 AUDIO PART S PDIF 15 7601_AUD0_SPDIF 15 3 40...

Page 57: ...BLOCK DIAGRAMS 1 OVERALL BLOCK DIAGRAM 3 43...

Page 65: ...MEMO...

Page 80: ...3 79 38 80 PRINTED CIRCUIT BOARD DIAGRAMS 1 MAIN P C BOARD TOP VIEW BOTTOM VIEW...

Page 81: ...3 81 3 82 2 SMPS P C BOARD TOP VIEW BOTTOM VIEW...

Page 82: ...3 M56 FPP SUB USB P C Boards TOP VIEW BOTTOM VIEW 3 83 3 84...

Page 83: ...3 85 3 86 4 FRONT TIMER P C BOARD TOP VIEW BOTTOM VIEW...

Page 84: ...6 WI FI P C BOARD TOP VIEW 5 ANALOG 7 1CH P C BOARD TOP VIEW 3 87 3 88 BOTTOM VIEW BOTTOM VIEW...

Page 85: ...3 89 3 90 MEMO MEMO...

Page 97: ...MEMO...

Page 98: ...4 12 4 11 CIRCUIT DIAGRAM...

Page 100: ...4 15 4 16 PRINTED CIRCUIT BOARD DIAGRAMS TOP VIEW...

Page 101: ...4 17 4 18 BOTTOM VIEW...