Theory of Operation

Chapter 3

SCXI-1100 User Manual

3-8

© National Instruments Corporation

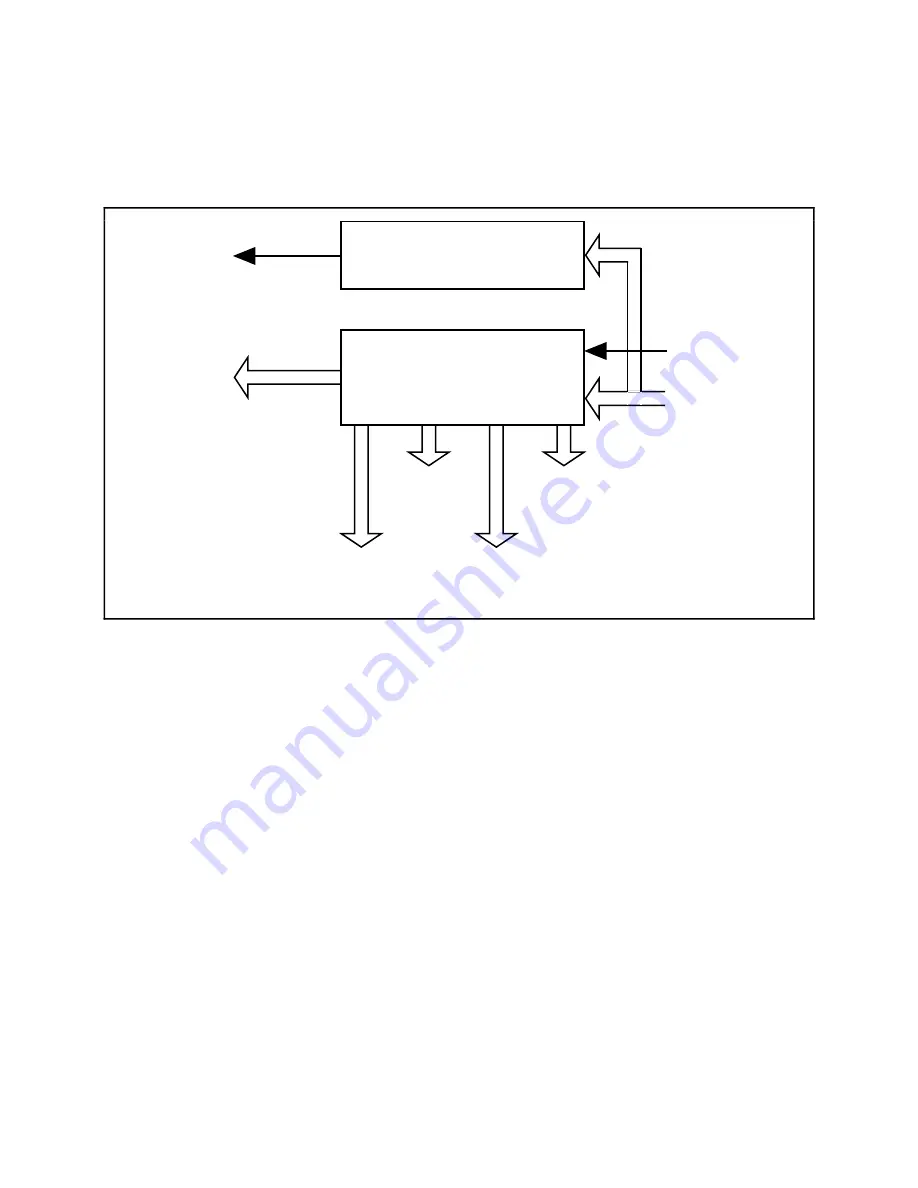

Digital Control Circuitry

Figure 3-5 diagrams the SCXI-1100 digital control circuitry.

Module ID Register

Configuration

Register

Serial Data Out

Input Channel

Select

PGIA

Gain

Select

Output

Stage

Control

Hardware

Scan

Control

SCANCLK

Path

Control

Buffered

Serial Data In

Buffered Digital

Control Signals

Figure 3-5. SCXI-1100 Digital Control Circuitry

The digital control circuitry section consists of the Configuration Register and the Module ID

Register.

The Configuration Register is a 3-byte serial-in parallel-out shift register. Data is received on the

MOSI line from either Slot 0 or the data acquisition board when SS* is enabled and D*/A

indicates data transfer (D*/A low). You use the Configuration Register for channel, gain,

calibration, and auto-zeroing selection, in addition to configuring the SCXI-1100 for scanning

options. All the control bits and the gain-select bits feed into a latch before being routed to the

rest of the module. The channel-select bits are taken directly from the shift register. Complete

descriptions of the register bits are given in Chapter 4, Register Descriptions. Writes to the

Configuration Register require the following steps:

1. Drive SS* low to enable communication with the board.

2. Drive D*/A low to indicate that the information sent on the MOSI line is data.

3. The serial data becomes available on MOSI. SPICLK clocks the data into the register.

4. Drive SS* high and D*/A high to indicate an end of communication. This latches the Configuration

Register bits.