6-2

|

ni.com

Chapter 6

Counters

Counter Timing Engine

Unlike analog input, analog output, digital input, and digital output, the cDAQ chassis counters

do not have the ability to divide down a timebase to produce an internal counter sample clock.

For sample clocked operations, an external signal must be provided to supply a clock source. The

source can be any of the following signals:

•

AI Sample Clock

•

AI Start Trigger

•

AI Reference Trigger

•

AO Sample Clock

•

DI Sample Clock

•

DI Start Trigger

•

DO Sample Clock

•

CTR

n

Internal Output

•

Freq Out

•

PFI

•

Change Detection Event

•

Analog Comparison Event

Not all timed counter operations require a sample clock. For example, a simple buffered pulse

width measurement latches in data on each edge of a pulse. For this measurement, the measured

signal determines when data is latched in. These operations are referred to as implicit timed

operations. However, many of the same measurements can be clocked at an interval with a

sample clock. These are referred to as sample clocked operations. Table 6-1 shows the different

options for the different measurements.

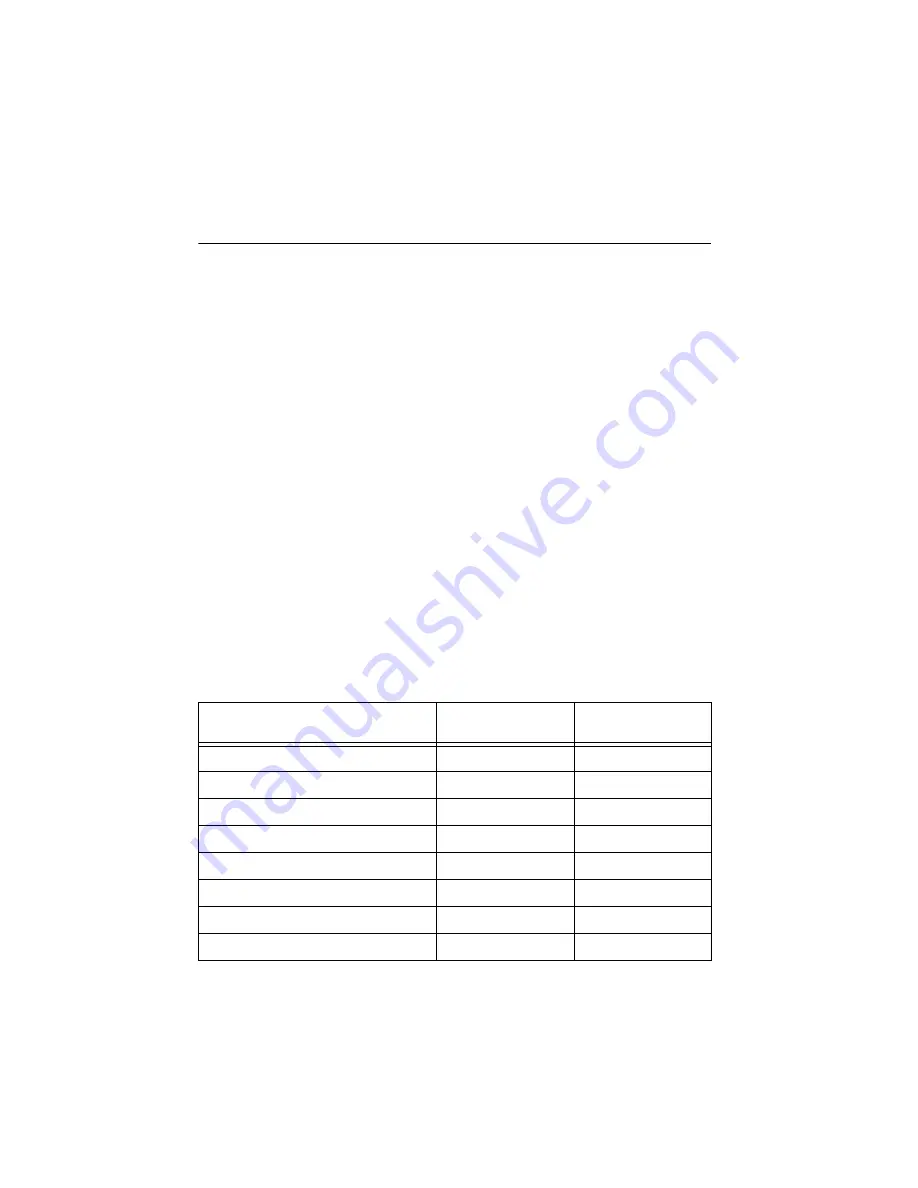

Table 6-1.

Counter Timing Measurements

Measurement

Implicit

Timing Support

Sample Clocked

Timing Support

Buffered Edge Count

No

Yes

Buffered Pulse Width

Yes

Yes

Buffered Pulse

Yes

Yes

Buffered Semi-Period

Yes

No

Buffered Frequency

Yes

Yes

Buffered Period

Yes

Yes

Buffered Position

No

Yes

Buffered Two-Signal Edge Separation

Yes

Yes

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com