Chapter 4

Signal Connections

PCI-4451/4452/4453/4454 User Manual

4-20

www.ni.com

Pretriggered data acquisition allows you to view data that you acquire

before the trigger of interest in addition to data you acquire after the trigger.

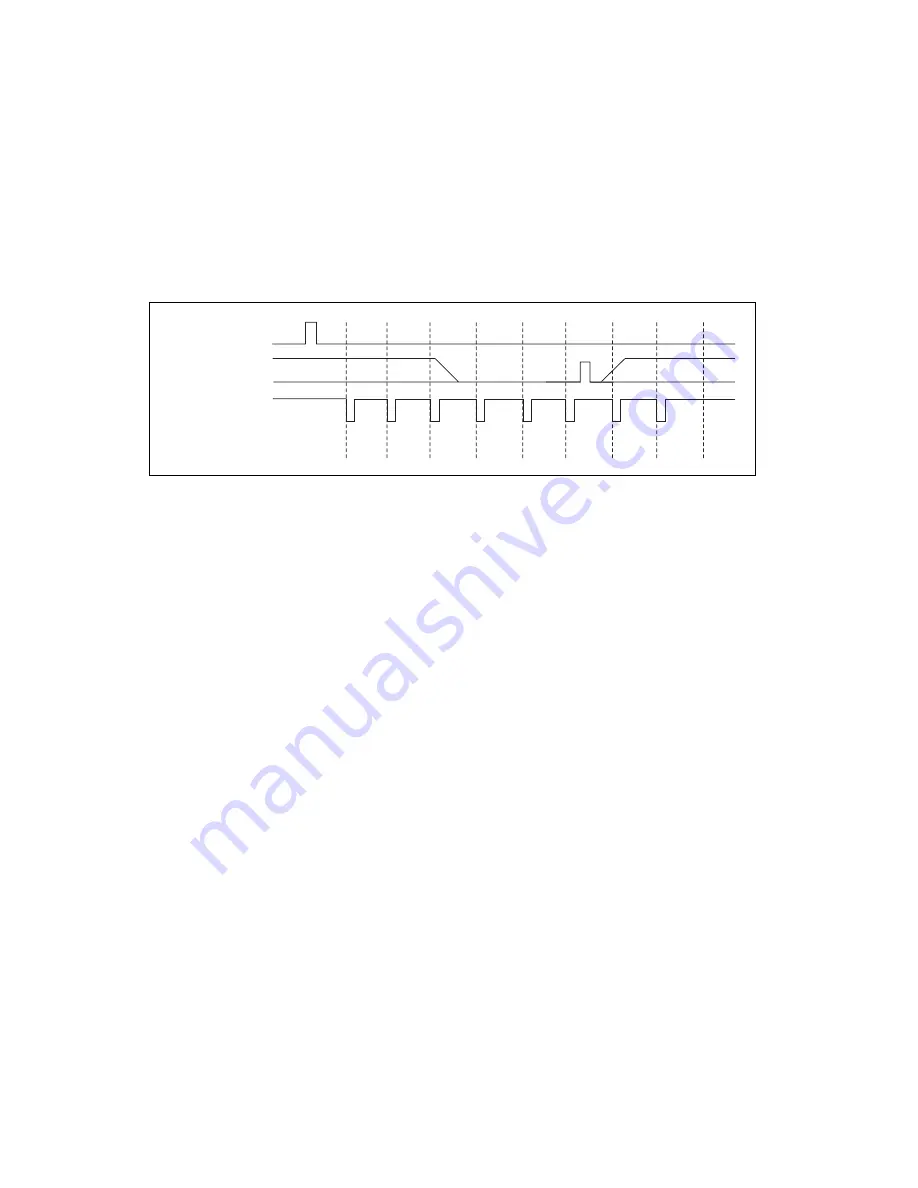

Figure 4-10 shows a typical pretriggered acquisition sequence. The

description for each signal shown in these figures is included in this

chapter.

Figure 4-10.

Typical Pretriggered Acquisition

PFI0/TRIG1 (EXT_TRIG) Signal

Any PFI pin can receive as an input the PFI0/TRIG1 (EXT_TRIG) signal,

which is available as an output on the PFI0/TRIG1 (EXT_TRIG) pin.

Refer to Figures 4-9 and 4-10 for the relationship of PFI0/TRIG1 to the

acquisition sequence.

As an input, the PFI0/TRIG1 signal is configured in the edge-detection

mode. You can select any PFI pin as the source for PFI0/TRIG1 and

configure the polarity selection for either rising or falling edge. The

selected edge of the PFI0/TRIG1 signal starts the data acquisition sequence

for both posttriggered and pretriggered acquisitions. The PCI-4451/4452

supports analog level triggering on the PFI0/TRIG1 pin. See Chapter 3,

, for more information on analog level triggering.

As an output, the PFI0/TRIG1 signal reflects the action that initiates an

acquisition sequence. This is true even if the acquisition is externally

triggered by another PFI signal. The output is an active high pulse with a

pulse width of 50 to 100 ns. This output is set to high-impedance at startup.

The device also uses the PFI0/TRIG1 signal to initiate pretriggered

acquisition operations. In most pretriggered applications, the PFI0/TRIG1

signal is generated by a software trigger. Refer to the

section for a complete description of the use of

PFI0/TRIG1 and PFI1/TRIG2 in a pretriggered acquisition operation.

Don't Care

0

1

2

3

1

0

2

2

2

TRIG1

TRIG2

CONVERT*

Sample Counter

Don't Care