Chapter 3

Analog Output Timing/Control

©

National Instruments Corporation

3-95

DAQ-STC Technical Reference Manual

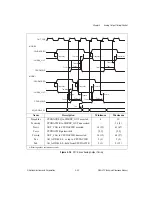

Figure 3-19.

Decoded Signal Timing

The numbers in parentheses are for DACWR<0..1>.

Name

Description

Minimum

Maximum

Tupld

UPDATE to LDACi asserted

1

4

TupldN

UPDATE to LDACi deasserted

1

5

Twrld

CPU/TMRDACWR to LDACi asserted

—

4 (0)

TwrldN

CPU/TMRDACWR to LDACi deasserted

—

4 (2)

Tckwr

OUT_CLK to DACWRi asserted

15

47

TckwrN

OUT_CLK to DACWRi deasserted

12

37

Taddr

TMRDACWR to da_addr change

3

10

Tascpu

AO_ADDR setup to CPUDACWR

3

9

Tahcpu

AO_ADDR hold from CPUDACWR

3

12

All timing values are in nanoseconds.

UPDATE

LDAC0

LDAC1

TMRDACWR

CPUDACWR

AO_ADDR0

DACWR0

DACWR1

OUT_CLK

Tupld

TupldN

Twrld

TwrldN Twrld

Tascpu

Tahcpu

Taddr

Tckwr

TckwrN

Tckwr

TckwrN

TwrldN