Chapter 4

Signal Connections

DIO 6533 User Manual

4-2

© National Instruments Corporation

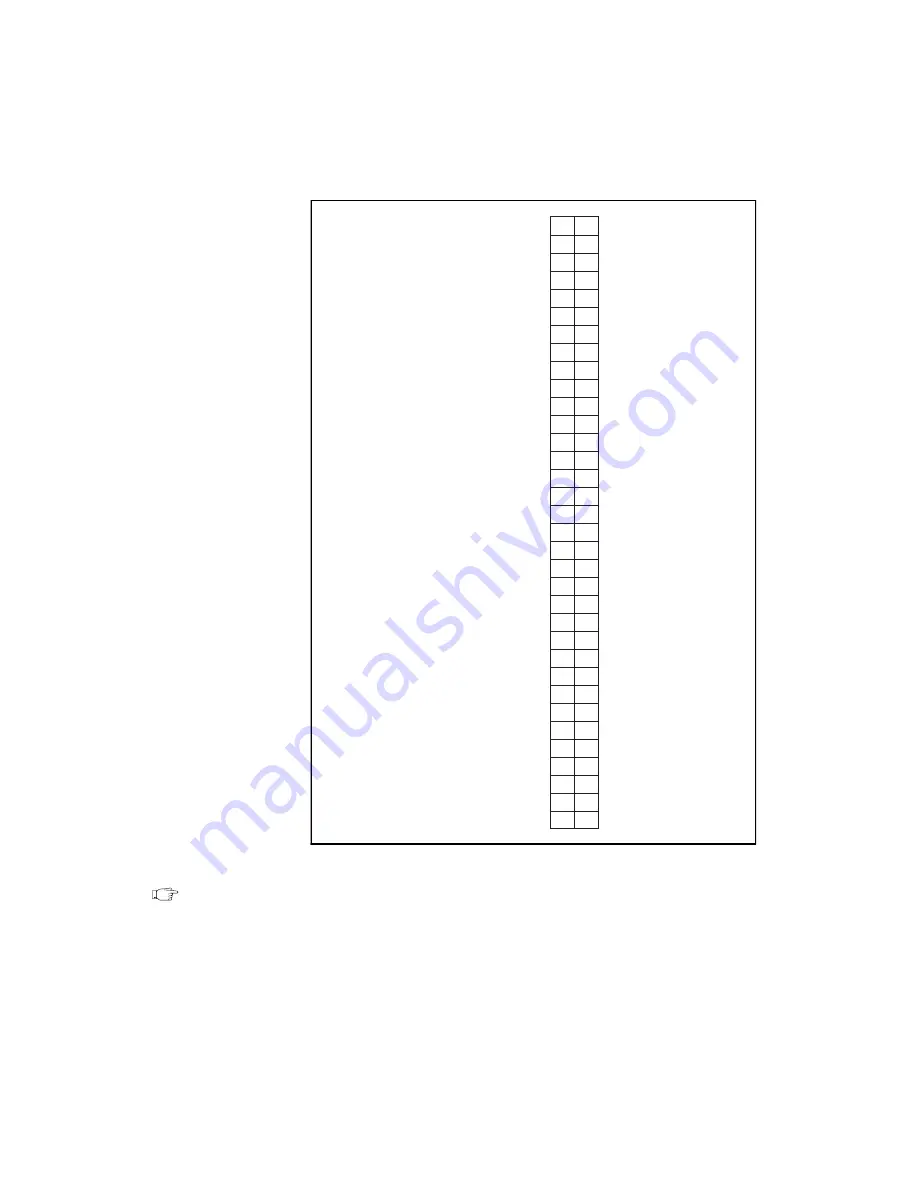

Figure 4-1. 6533 Device I/O Connector Pin Assignments

Note:

In Figure 4-1, the * indicates that you can reverse the pin assignments of

the ACK1 (STARTTIG1) and REQ1 pins, or the ACK2 (STARTTIG2) and

REQ2 pins, with software. This can be useful when performing two-way

ACK/REQ handshaking between two 6533 devices over an SH68-68-D1 or

similar cable, because it allows you to connect one device’s ACK pin to the

+5 V

REQ1*

ACK1 (STARTTRIG1)*

STOPTRIG1

PCLK1

PCLK2

STOPTRIG2

ACK2 (STARTTRIG2)*

REQ2*

DIOA0

GND

DIOA3

DIOA4

GND

DIOA7

DIOB0

DIOB1

GND

RGND

GND

DIOB6

DIOB7

DIOC0

GND

DIOC3

DIOC4

GND

DIOC7

DIOD0

GND

DIOD3

DIOD4

GND

DIOD7

RGND

GND

DPULL

CPULL

GND

GND

RGND

GND

GND

DIOA1

DIOA2

GND

DIOA5

DIOA6

GND

GND

DIOB2

DIOB3

DIOB4

DIOB5

GND

RGND

DIOC1

DIOC2

GND

DIOC5

DIOC6

GND

DIOD1

DIOD2

GND

DIOD5

DIOD6

GND

1

35

2

36

3

37

4

38

5

39

6

40

7

41

8

42

9

43

10 44

11 45

12 46

13 47

14 48

15 49

16 50

17 51

18 52

19 53

20 54

21 55

22 56

23 57

24 58

25 59

26 60

27 61

28 62

29 63

30 64

31 65

32 66

33 67

34 68