B-22

|

ni.com

Appendix B

Timing Diagrams

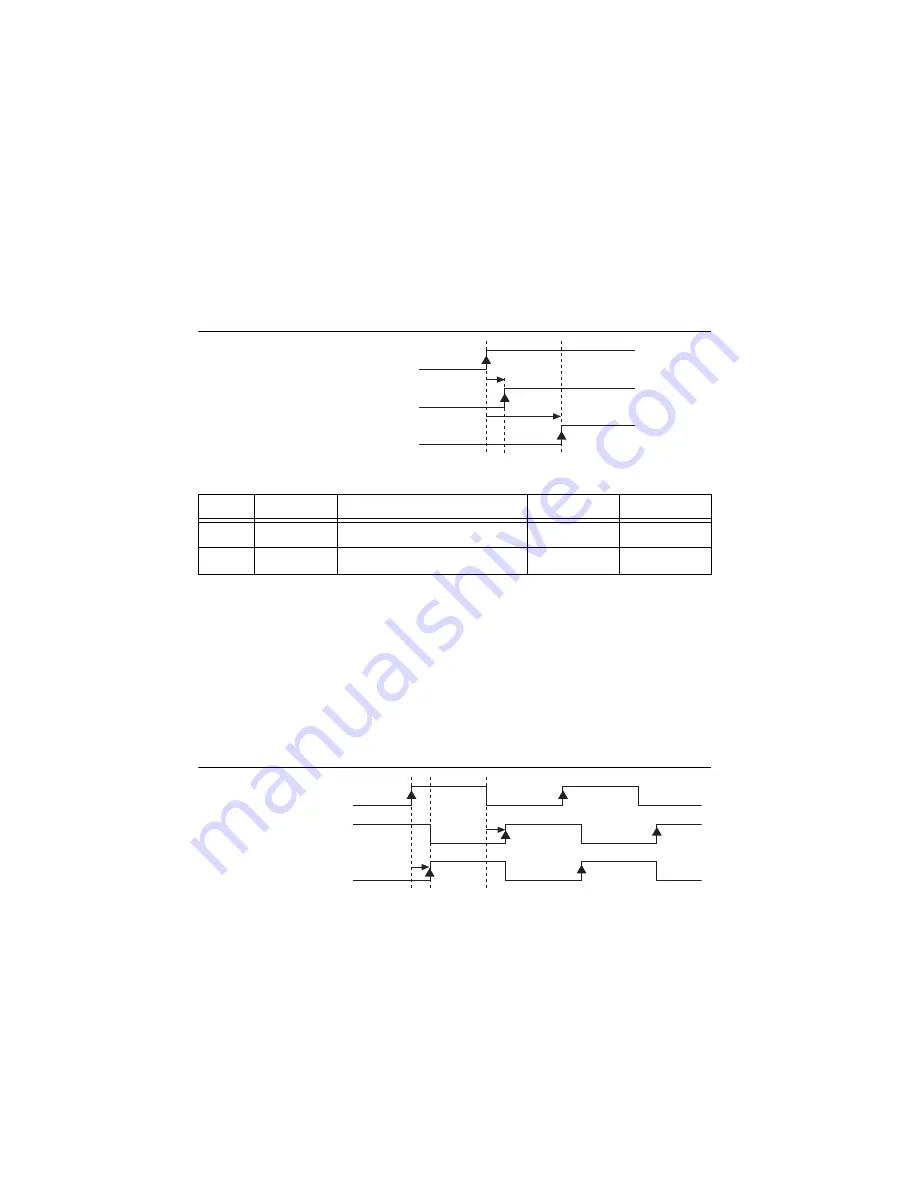

Internal Analog Output Timing

The analog output timer has two internal clocks that are referenced—Sample Clock Timebase

and Sync Sample Clock Timebase. How they are generated depends on how the analog output

timer is configured. If the analog output timing engine is configured to operate with an external

Sample Clock, analog output internal clock timing can be derived from Table B-13.

Figure B-24.

External Update Source Clock Insertions Timing Diagram

If the Sample Clock is being generated by dividing down the Sample Clock Timebase, the analog

output generation is timed from the output of the UI counter. The signal Sample Clock Timebase

can be an external signal. When the analog output timing engine operates in this mode, it is

assumed that the source signal for the Sample Clock timebase is a free-running clock, so the

Sync Sample Clock Timebase is the inverted version of Sample Clock Timebase. Configuring

the analog output timing engine for rising edge operation will cause the external signals to be

synchronized on the falling edge of the Sample Clock Timebase, which corresponds to the rising

edge of Sync Sample Clock Timebase.

Figure B-25.

Sample Clock Timebase and the Sync Sample Clock Timebase

Timing Diagram

Table B-13.

External Update Source Clock Insertions Timing

Time

From

To

Min (ns)

Max (ns)

t

2

Signal_i

Sample Clock Timebase

11.6

30.0

t

3

Signal_i

Sync Sample Clock Timebase

1.5

7.0

Signal_i

Sample Clock Timebase

Sync Sample Clock Timebase

t

2

t

3

Signal_i

Sample Clock Timebase

Sync Sample Clock Timebase

t

5

t

4

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com