©

National Instruments Corporation

11

NI 5412 Specifications

CLK IN

(Sample Clock and Reference Clock Input, Front Panel Connector)

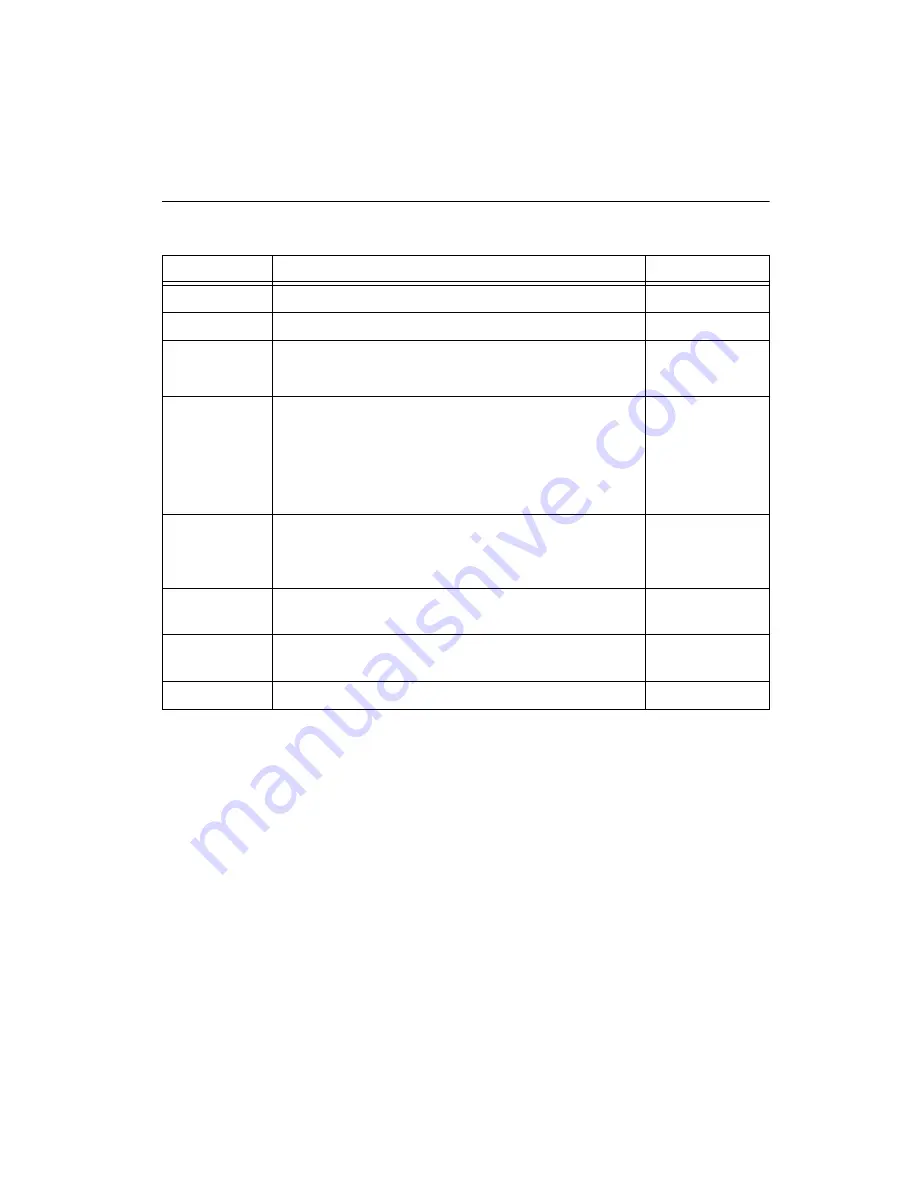

Table 5.

Specification

Value

Comments

Connector

SMB (jack)

—

Direction

Input

—

Destinations

1. Sample Clock

2. PLL Reference Clock

—

Frequency

Range

1 MHz to 105 MHz (Sample Clock destination and

sine waves)

200 kHz to 105 MHz (Sample Clock destination and

square waves)

5 MHz to 20 MHz (PLL Reference Clock destination)

—

Input Voltage

Range

Sine wave: 0.65 V

pk-pk

to 2.8 V

pk-pk

into 50

Ω

(0 dBm to +13 dBm)

Square wave: 0.2 V

pk-pk

to 2.8 V

pk-pk

into 50

Ω

—

Maximum

Input Overload

±10 V

—

Input

Impedance

50

Ω

—

Input Coupling

AC

—