10

|

ni.com

|

NI 5782R User Manual and Specifications

–

Internal Sample Clock locked to an external Reference Clock through

IoModSyncClock

–

External Sample Clock through IoModSyncClock

This CLIP also contains an engine to program the CLK chip, ADCs, and DACs, either

through predetermined settings for an easier instrument setup, or through a raw SPI address

and data signals for a more advanced setup.

Refer to the

NI FlexRIO Help

for more information about NI FlexRIO CLIP items, how to

configure the NI 5782 with a socketed CLIP, and for a list of available socketed CLIP signals.

Connecting Cables

•

Use any 50

Ω

SMA cable to connect signals to the connectors on the front panel of your

NI 5782.

•

Use the SHH19-H19-AUX cable (NI part number: 152629-01 or 152629-02)

to connect to

the DIO and PFI signals on the AUX I/O connector.

For more information about connecting I/O signals on your device, refer to the

Appendix A:

Specifications

section of this document.

Clocking

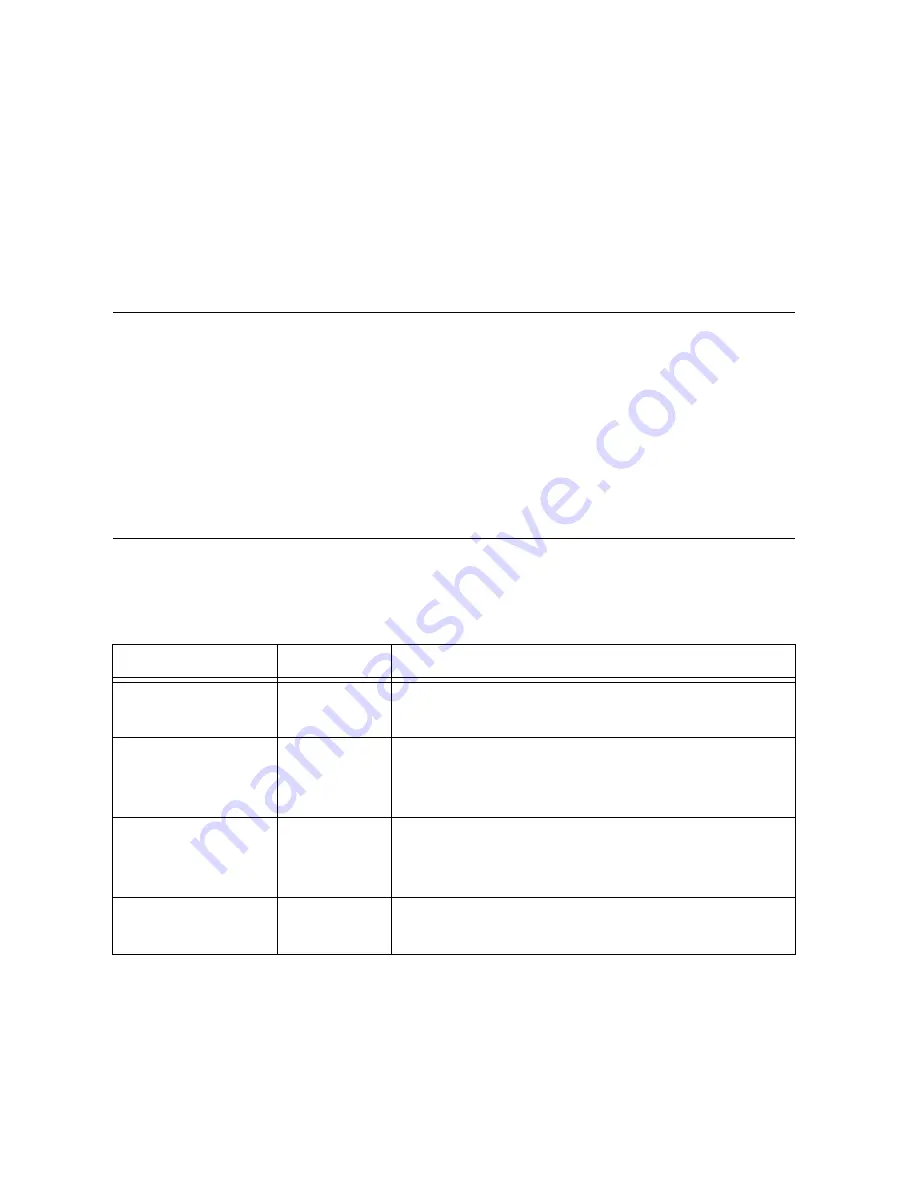

The NI 5782 clocks control the sample rate and other timing functions on the device. Table 4

contains information about the possible NI 5782 clock resources.

Table 4.

NI 5782 Clock Sources

Clock

Frequency

S

ource Options

Internal Clock

PLL Off

500 MHz

The internal voltage-controlled oscillator (VCO) acts

as a free-running clock.

Internal Clock

PLL On

(IoModSyncClock)

500 MHz

The internal VCO locks to PXI_CLK10 through

IoModSyncClock, which is available only through

the backplane of NI PXIe-796

x

R

devices.

Internal Clock

PLL On

(CLK IN)

500 MHz

The internal VCO locks to an external Reference

Clock (10 MHz). Connect the external Reference

Clock through the CLK IN front panel connector.

External Clock

(CLK IN)

250 MHz to

1 GHz

Connect an external Sample Clock through the

CLK IN front panel connector.