Chapter 1

Getting Started

1-10

ni.com

Local bus signals may range from high-speed TTL signals to analog signals

as high as 42 V.

Initialization software uses the configuration information specific to each

adjacent peripheral module to evaluate local bus compatibility.

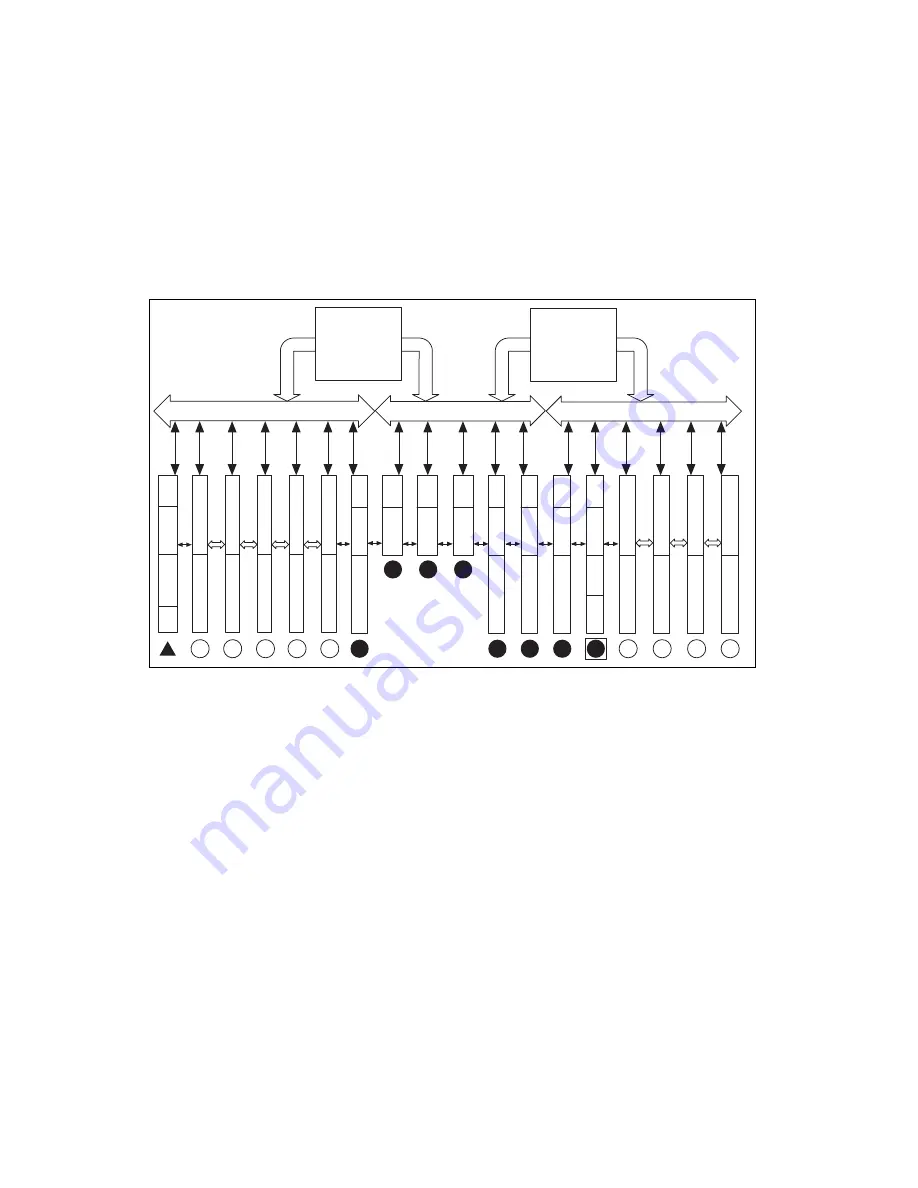

Figure 1-4.

PXI Trigger Bus and Local Bus Connectivity Diagram

PXI Trigger Bus

All slots on the same PXI bus segment share eight PXI trigger lines. You

can use these trigger lines in a variety of ways. For example, you can use

triggers to synchronize the operation of several different PXI peripheral

modules. In other applications, one module located in the system timing

slot can control carefully timed sequences of operations performed on other

modules in the system. Modules can pass triggers to one another, allowing

precisely timed responses to asynchronous external events the system is

monitoring or controlling.

The PXI trigger lines from adjacent PXI trigger bus segments can be routed

in either direction across the PXI trigger bridges through buffers. This

allows you to send trigger signals to, and receive trigger signals from, every

slot in the chassis. Static trigger routing (user-specified line and directional

P2

P1

XP4

XP

3

TP2

TP1

P2

P1

P2

P1

P2

P1

P1

P1

P1

XP4

XP

3

XP4

XP

3

XP4

XP

3

XP4

XP

3

XP4

XP

3

XP4

XP

3

XP4

XP

3

P2

P1

P2

P1

P2

P1

P2

P1

P2

P1

P1

XP4

XP

3

XP2

XP1

PXI_LB6

PXI_LB6

PXI_LB6

PXI_LB6

PXI_LB6

PXI_LB6

PXI_LB6

PXI_LB6

PXI_LB6

PXI_LB6

PXI_LB (12:0)

PXI_LB (12:0)

PXI_LB (12:0)

PXI_LB (12:0)

PXI_LB (12:0)

PXI_LB (12:0)

PXI_LB (12:0)

PXI

Trigger B

us

B

u

ffer Bridge

PXI

Trigger B

us

B

u

ffer Bridge

PXI Trigger B

us

S

egment 1

PXI Trigger B

us

S

egment 2

PXI Trigger B

us

S

egment

3

1

8

9

10

7

H

11

H

H

12

H

1

3

14

15

6

5

4

3

2

16

17

1

8