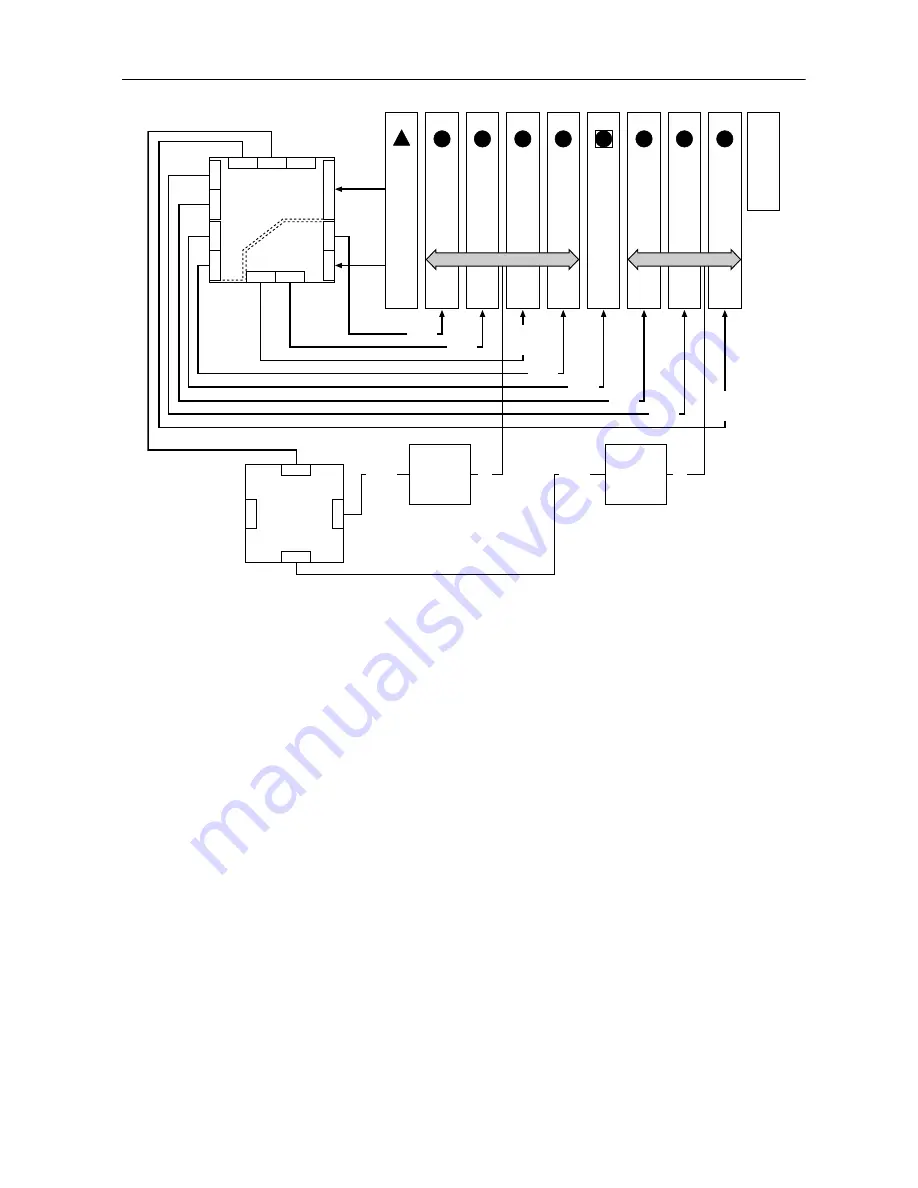

Figure 3. PXIe-1092 PCI Express Backplane Diagram

3

H

2

H

4

H

5

H

7

H

8

H

9

H

1

Station 0

Station 1

Station 1

Virtual

Switch 0

Secondary

PCIe Switch

Primary

PCIe Switch

Expansion Slot

Virtual

Switch 1

Station 2

Station 4

Station 5

P

or

t 0

P

or

t 1

P

or

t 0

P

or

t 18

P

or

t 17

P

or

t 20

P

or

t 21

Port 4 Port 5

Port 12 Port 13 Port 14

32-bit, 33 MHz PCI

32-bit, 33 MHz PCI

6

P

or

t 4

P

or

t 1

Port 0

Port 5

PCI

Bridge #2

Gen3 x16

Gen3 x8

Gen3 x8

Gen3 x8

Gen3 x8

Gen3 x8

Gen3 x8

Gen3 x8

Gen3 x8

Gen3 x8

Gen2 x1

PCI

Bridge #1

Gen1 x1

PCI

Gen1 x1

PCI

System Timing Slot

The system timing slot is slot 6. The system timing slot accepts the following peripheral

modules:

•

A PXI Express System Timing Module with x8, x4, or x1 PCI Express link to the system

slot through a PCI Express switch. Each PXI Express peripheral or hybrid peripheral slot

can link up to a Gen-3 x8 PCI Express, providing a maximum nominal single-direction

bandwidth of 8 GB/s.

•

A PXI Express Peripheral with x8, x4, or x1 PCI Express link to the system slot through a

PCI Express switch.

•

A CompactPCI Express Type-2 Peripheral with x8, x4, or x1 PCI Express link to the

system slot through a PCI Express switch.

The system timing slot has three (3) dedicated differential pairs (PXIe_DSTAR) connected

from the TP1 and TP2 connectors to the XP3 connector for each PXI Express hybrid

peripheral slot, as well as routed back to the XP3 connector of the system timing slot, as

shown in the following figure. You can use the PXIe_DSTAR pairs for high-speed triggering,

synchronization, and clocking. Refer to the

PXI Express Specification

for details.

The system timing slot also has a single-ended (PXI Star) trigger connected to every slot.

Refer to the following figure for more details.

8

|

ni.com

|

PXIe-1092 User Guide