Nations Technologies Inc.

Tel

:

+86-755-86309900

:

info@nationstech.com

Address: Nations Tower, #109 Baoshen Road, Hi-tech Park North.

Nanshan District, Shenzhen, 518057, P.R.China

143

/

631

Offset

Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Reset Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

078h

DMA_MADDR6

ADDR[31:0]

Reset Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

07Ch

DMA_CHSEL6

Reserved

CH_SEL[5:0]

Reset Value

0

0

0

0

0

0

080h

DMA_CHCFG7

Reserved

M

E

M

2M

E

M

P

R

IOL

VL

[1:

0]

M

S

IZ

E

[1:0

]

P

S

IZ

E

[1:0]

M

INC

P

INC

C

IR

C

DI

R

E

R

R

IE

HT

XI

E

T

XC

IE

C

HE

N

Reset Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

084h

DMA_TXNUM7

Reserved

NDTX[15:0]

Reset Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

088h

DMA_PADDR7

ADDR[31:0]

Reset Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

08Ch

DMA_MADDR7

ADDR[31:0]

Reset Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

090h

DMA_CHSEL7

Reserved

CH_SEL[5:0]

Reset Value

0

0

0

0

0

0

094h

DMA_CHCFG8

Reserved

M

E

M

2M

E

M

P

R

IOL

VL

[1:

0]

M

S

IZ

E

[1:0

]

P

S

IZ

E

[1:0]

M

INC

P

INC

C

IR

C

DI

R

E

R

R

IE

HT

XI

E

T

XC

IE

C

HE

N

Reset Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

098h

DMA_TXNUM8

Reserved

NDTX[15:0]

Reset Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

09Ch

DMA_PADDR8

ADDR[31:0]

Reset Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0A0h

DMA_MADDR8

ADDR[31:0]

Reset Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0A4h

DMA_CHSEL8

Reserved

CH_SEL[5:0]

Reset Value

0

0

0

0

0

0

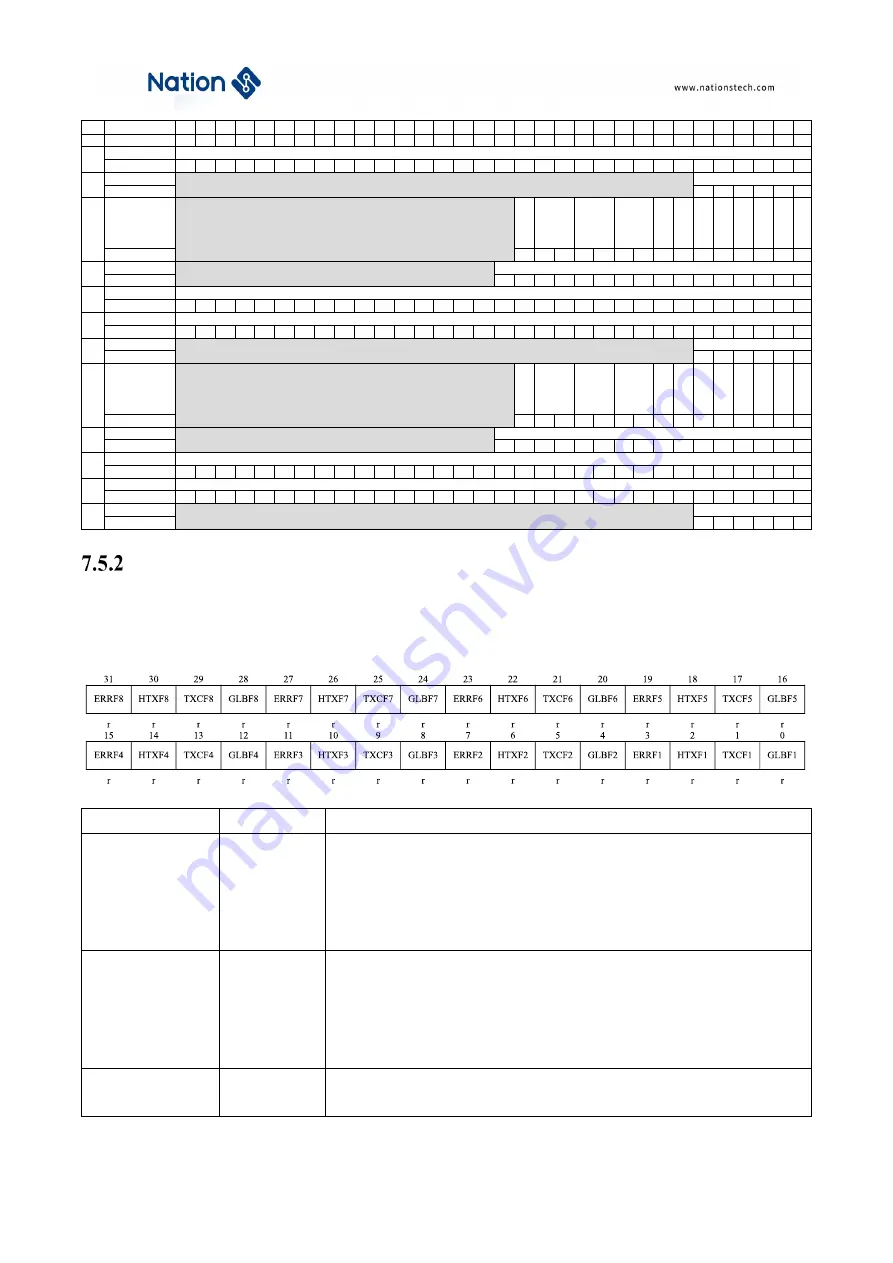

DMA interrupt status register (DMA_INTSTS)

Address offset: 0x00

Reset value: 0x0000 0000

Bit field

Name

Description

31/27/23/19/15/11/7/3

ERRFx

Transfer error flag for channel x (x=1…8).

Hardware sets this bit when transfer error happen. This bit is cleared by software by

writing ‘1’ to DMA_INTCLR.CERRFx bit.

0: Transfer error no happened on channel x.

1: Transfer error happened on channel x.

30/26/22/18/14/10/6/2

HTXFx

Half transfer flag for channel x (x=1…8).

Hardware sets this bit when half transfer is done. This bit is cleared by software by

writing ‘1’ to DMA_INTCLR.CHTXFx bit.

0: Half transfer not yet done on channel x.

1: Half transfer was done on channel x.

29/25/21/17/13/9/5/1

TXCFx

Transfer complete flag for channel x (x=1…8).

Hardware sets this bit when transfer is done. This bit is cleared by software by writing