Nations Technologies Inc.

Tel

:

+86-755-86309900

:

info@nationstech.com

Address: Nations Tower, #109 Baoshen Road, Hi-tech Park North.

Nanshan District, Shenzhen, 518057, P.R.China

625

/

631

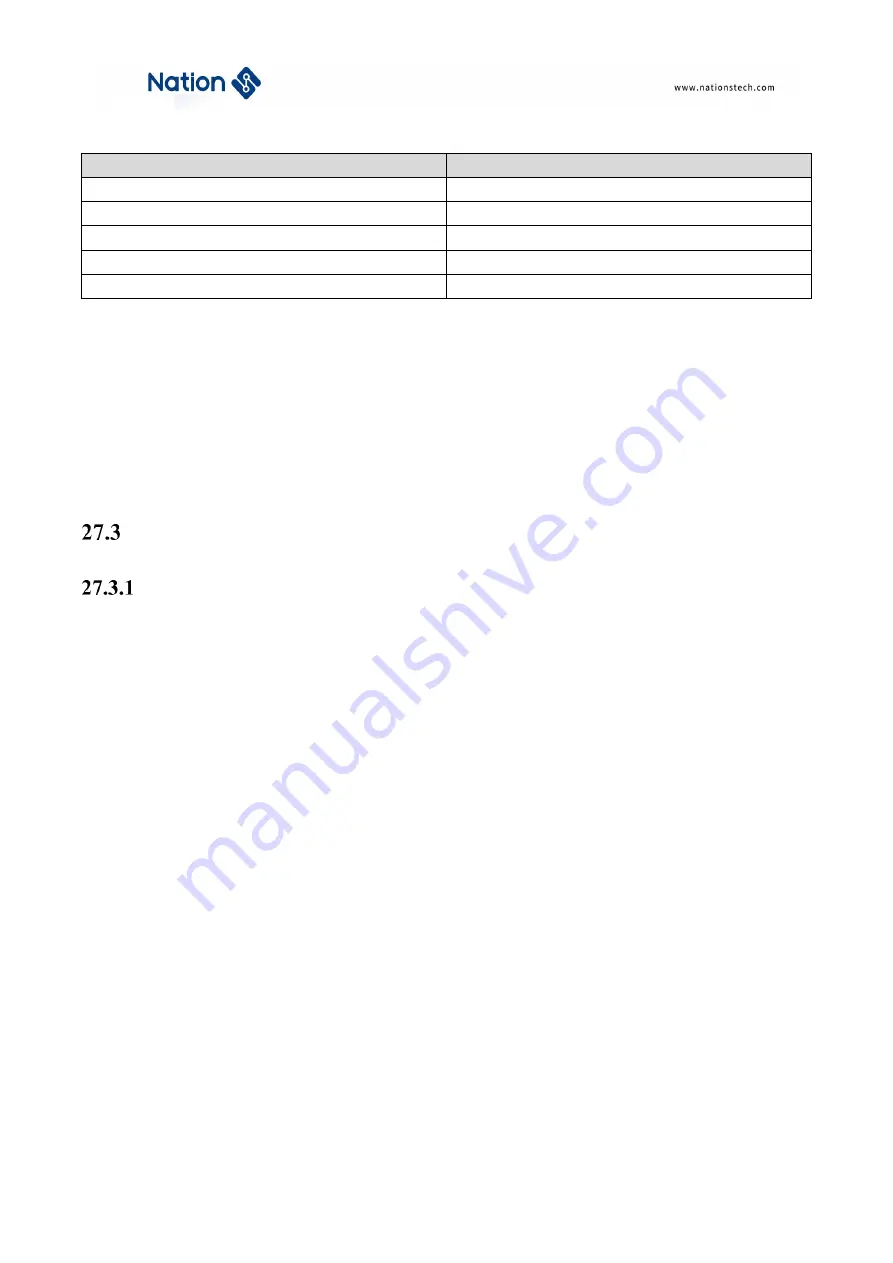

Table 27-1 Debug port pin

Debug port

Pin allocation

JTMS/SWDIO

PA13

JTCK/SWCLK

PA14

JTDI

PA15

JTDO

PB3

NJTRST

PB4

When both JTAG debugging interface and SWD debugging interface are enabled, the 5-wire JTAG debugging

interface will be used by default after reset.

When using JTAG interface, users can not use NJTRST pin. In this case, NJTRST pin (PB4, internal hardware

pull-up) can be used as a general-purpose GPIO.

When SWD interface is used, three pins JTDI (PA15), JTDO (PB3) and NJTRST (PB4) can be used as general

GPIO.

When the debugging function is not used, the above five pins can be used as general-purpose GPIO.

MCU debug function

Low-power mode debug support

N32G43x provides various low-power modes (See chapter Power control (PWR)for details). By default, if the MCU

enters SLEEP, STOP2, or STANDBY mode while the application is using the debug feature, the debug connection

will be lost. When debugging, make sure that the FCLK and HCLK of the core are turned on, and provide the

necessary clock for the core debugging. Users can perform software debugging in low power mode according to

specific operations.

To do this, a debugger or software first needs to configure the debug control registers associated with the low power

modes:

DBG_SLEEP mode:

The DBG_CTRL.SLEEP bit needs to be configured to provide HCLK with the same clock as provided to FCLK

(ie: the original configured system clock).

DBG_STOP mode:

The DBG_CTRL.STOP bit needs to be configured to start the internal RC oscillator to provide the clock for

HCLK and FCLK.

DBG_STANDBY mode:

The DBG_CTRL.STDBY bit needs to be configured to start the internal RC oscillator to provide the clock for

HCLK and FCLK.