32

Chapter 4

Differences between Target Device and Emulation Board

Preliminary User’s Manual U16345EE1V0UM00

4.7 AV

DD

, AV

SS

pins

AV

DD

and AV

SS

pins of the I/O chip on the emulation board can be disconnected from the target con-

nector. ADC values and the load on AV

DD

and AV

SS

pins may differ in that case.

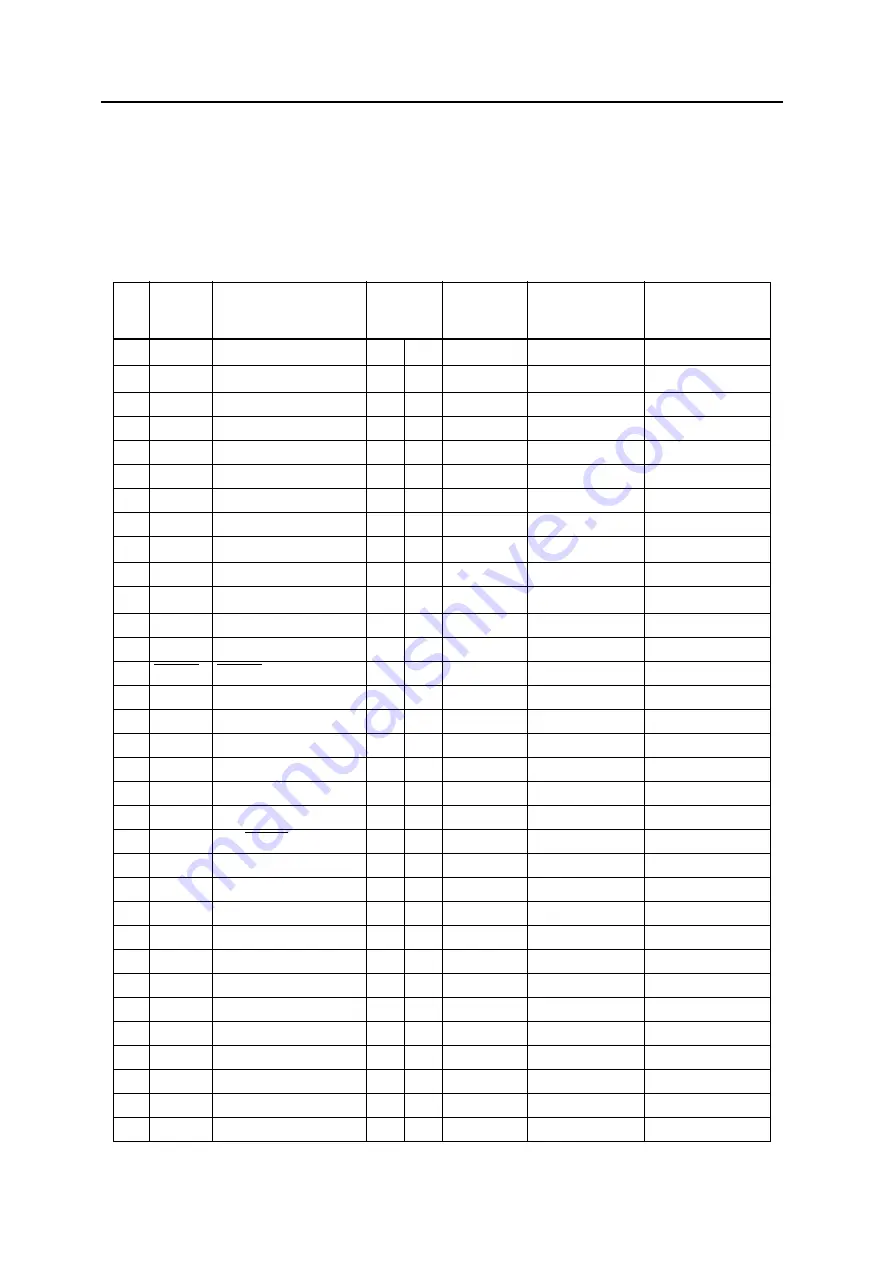

Table 4-1:

Pin list according to their emulation location (1/3)

100

Pin

Top pin

name

Pin Function

default I/O

single chip

Emulated by

Venus chip

Emulated by

FPGA via Level

Shifter

Alternative

connected to:

1 AV

DD

AV

DD

S

Venus

internal

2 AV

SS

AV

SS

S

Venus

internal

3 P00

P00/INTP0

I

Venus

4 P01

P01/INTP1

I

Venus

5 P02

P02/INTP2

I

Venus

6 P03

P03/INTP3

I

Venus

7 P04

P04/INTP4

I

Venus

8 P05

P05/INTP5

I

Venus

9 V

DD50

V

DD50

S

buffered

10 REGC0

REGC0

S

not connected

11 V

SS30

V

SS30

S

Ground

12 X1

X1

I

not connected

13 X2

X2

O

not connected

14 RESET

RESET

I

buffered

15 XT1

XT1

I

not connected

16 XT2

XT2

O

not connected

17 NMI

NMI

I

Venus

18 P06

P06/INTP6

I

Venus

19 P10

P10/SI00

I

Venus

20 P11

P11/SO00

I

Venus

21 P12

P12/SCK00

I

Venus

22 P13

P13/RXD60/INTP7

I

Venus

23 P14

P14/TXD60

I

Venus

24 P15

P15

I

Venus

25 P40

P40/KR0

I

Venus

26 P41

P41/KR1/TIG00

I

Venus

27 P42

P42/KR2/TIG01/TOG01 I

Venus

28 P43

P43/KR3/TIG02/TOG02 I

Venus

29 P44

P44/KR4/TIG03/TOG03 I

Venus

30 P45

P45/KR5/TIG04/TOG04 I

Venus

31 P46

P46/KR6/TIG05

I

Venus

32 P47

P47/KR7

I

Venus

33 P50

P50

I

Venus

Summary of Contents for IE-703242-G1-EM1

Page 6: ...6 Preliminary User s Manual U16345EE1V0UM00 ...

Page 8: ...8 Preliminary User s Manual U16345EE1V0UM00 ...

Page 10: ...10 Preliminary User s Manual U16345EE1V0UM00 ...

Page 18: ...18 Preliminary User s Manual U16345EE1V0UM00 MEMO ...

Page 28: ...28 Preliminary User s Manual U16345EE1V0UM00 MEMO ...

Page 30: ...30 Preliminary User s Manual U16345EE1V0UM00 MEMO ...

Page 36: ...36 Preliminary User s Manual U16345EE1V0UM00 MEMO ...

Page 40: ...40 Preliminary User s Manual U16345EE1V0UM00 ...

Page 42: ......