5-16 Problem Solving

MESSAGE

DESCRIPTION

System CMOS checksum bad - run

SETUP

The system CMOS has been corrupted or incorrectly modified, perhaps

by an application program that changes data stored in CMOS. Run

Setup and reconfigure the system either by getting the default values or

making your own selections.

System RAM failed at offset: nnnn*

The system RAM failed at offset nnnn of the 64K block at which the

error was detected.

nnnn System RAM Passed

Where nnnn is the amount of system RAM in kilobytes successfully

tested.

System timer error*

The timer test failed. Requires repair of the system board.

UMB upper limit segment address:

nnnn

Displays the address nnnn of the upper limit of the Upper Memory

Blocks, indicating released segments of the BIOS which may be

reclaimed by a virtual memory manager.

Video BIOS shadowed

The video BIOS is successfully copied to shadow RAM.

•

If your system displays this message, write down the message and notify your customer representative. If your system fails after

you made changes in the BIOS Setup menus, you may be able to correct the problem by entering Setup and restoring the original

values.

Messages and Beep Codes

Whenever a recoverable error occurs during POST, BIOS displays a message on the

video display screen and causes the speaker to beep twice as the message appears.

BIOS also issues a beep code (one long tone followed by two short tones) during POST

if the video configuration fails or if an external ROM module does not checksum to

zero.

At the beginning of each POST test routine, the BIOS outputs the test point error code

to I/O address 80h. If the BIOS detects a terminal error condition, it halts POST after

issuing a terminal error beep code signifying the test point code and attempting to

display the test point error code on the upper left corner of the display screen. BIOS

derives the beep code from the test point error code.

For example, a test point error code of 16 is indicated by a 1-2-2-3 beep code (a single

beep, a burst of two beeps, a burst of two beeps, and a burst of three beeps). In addition,

BIOS writes a value of 16 on the upper left corner of the display screen and to I/O port

80h to enable debugging tools to identify the area of failure.

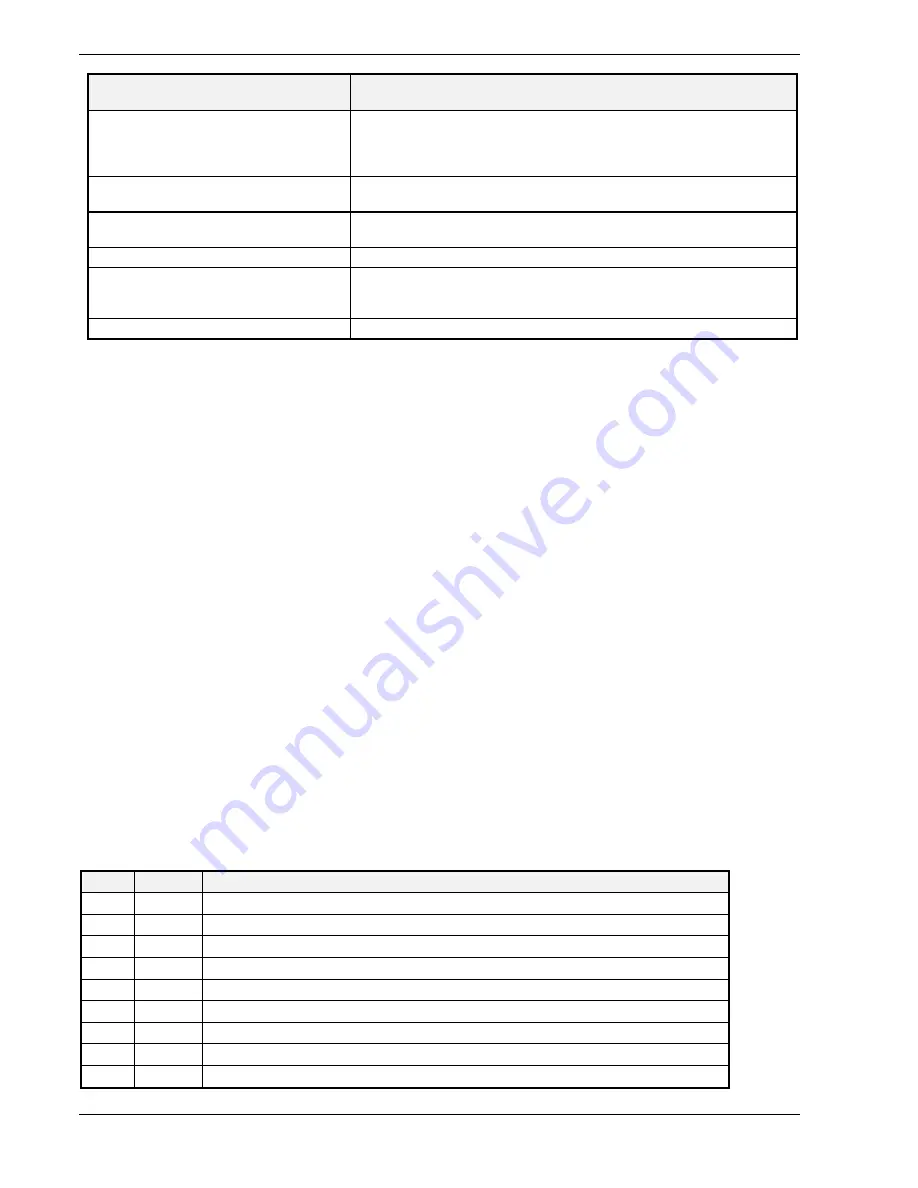

Table 5-3 is a list of the test point error codes written at the start of each POST test and

the beep codes issued for terminal errors.

Table 5-3 POST Tests

Code

Beeps

POST Routine Description

02

1-1-1-3

Verify Real Mode

04

1-1-2-1

Get CPU type

06

1-1-2-3

Initialize system hardware

08

1-1-3-1

Initialize chipset registers with initial POST values

09

1-1-3-2

Set in POST flag

0A

1-1-3-3

Initialize CPU registers

0C

1-1-4-1

Initialize cache to initial POST values

0E

1-1-4-3

Initialize I/O

10

1-2-1-1

Initialize Power Management

Summary of Contents for MC2200

Page 1: ... U s e r s G u i d e Server MC2200 ...

Page 2: ...xxx ...

Page 3: ... U s e r s G u i d e Server MC2200 ...

Page 13: ...Using This Guide xi ...

Page 14: ......

Page 26: ...Packard Bell NEC ...

Page 34: ...2 8 Setting Up the System Figure 2 4 Opening the Front Door ...

Page 66: ...Packard Bell NEC ...

Page 96: ...Packard Bell NEC ...

Page 116: ......

Page 117: ...A System Cabling System Cabling Static Precautions Standard Configuration RAID Configuration ...

Page 124: ...Packard Bell NEC ...

Page 125: ...B System Status Hardware Support Information ...

Page 136: ...10 Glossary ...

Page 141: ...xx ...

Page 142: ... 904455 01 ...