155

CHAPTER 8 16-BIT TIMER/EVENT COUNTER

User’s Manual U12697EJ3V0UM

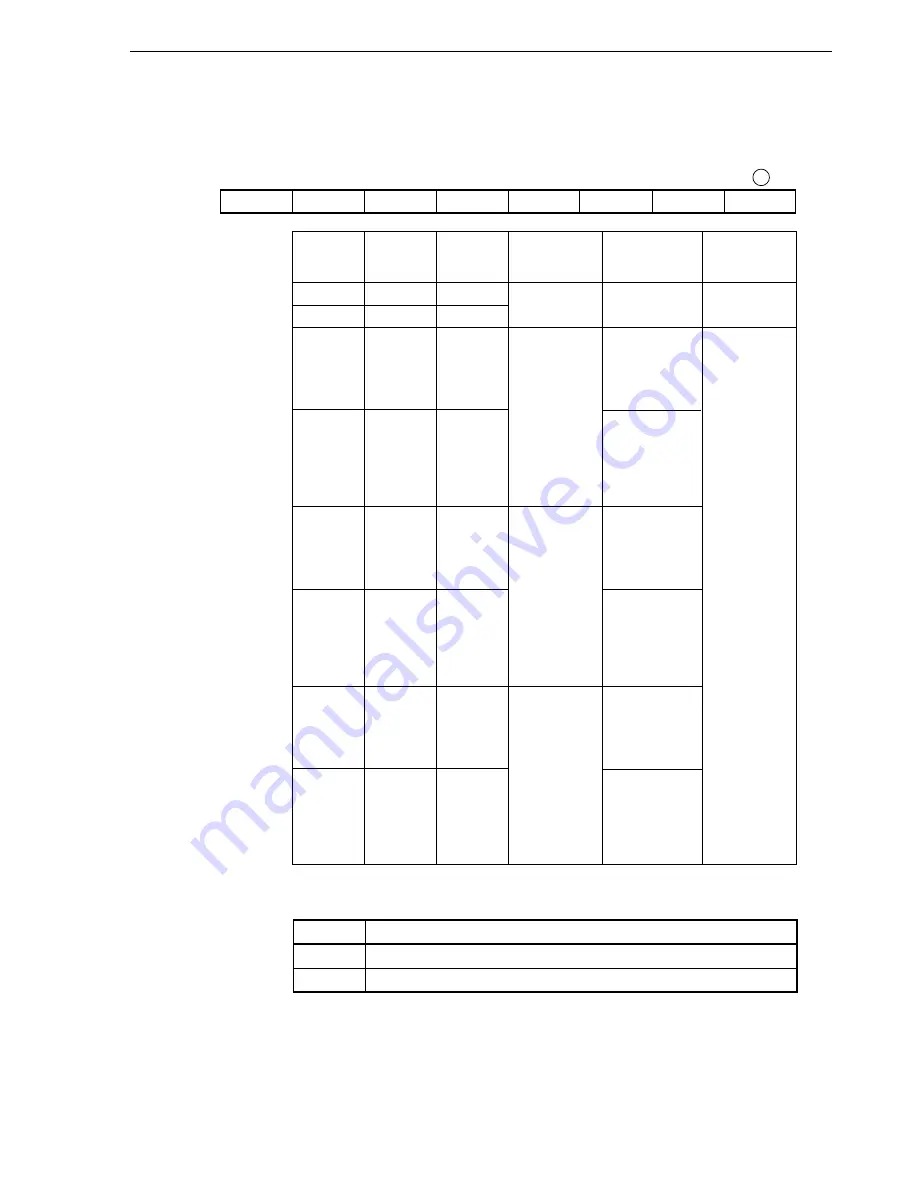

Figure 8-2. Format of 16-Bit Timer Mode Control Register 0 (TMC0)

Address: 0FF18H After reset: 00H R/W

Symbol

7

6

5

4

3

2

1

0

TMC0

0

0

0

0

TMC03

TMC02

TMC01

OVF0

TMC03

TMC02

TMC01

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

0VF0

Detection of overflow of 16-bit timer counter 0

0

Overflows.

1

Does not overflow.

Selection of

operation mode/

clear mode

Selection of TO0

output timing

Generation of

interrupt

Not affected

Match between

TM0 and CR00

or match

between TM0

and CR01

Match between

TM0 and CR00,

match between

TM0 and CR01,

or valid edge of

TI00

Match between

TM0 and CR00

or match

between TM0

and CR01

Match between

TM0 and CR00,

match between

TM0 and CR01,

or valid edge of

TI00

Match between

TM0 and CR00

or match

between TM0

and CR01

Match between

TM0 and CR00,

match between

TM0 and CR01,

or valid edge of

TI00

Does not

generate.

Free running

mode

Clears and

starts at valid

edge of TI00.

Clears and

starts on match

between TM0

and CR00.

Generates on

match between

TM0 and CR00

and match

between TM0

and CR01.

Operation stop

(TM0 is cleared

to 0).