162

CHAPTER 8 16-BIT TIMER/EVENT COUNTER

User’s Manual U12697EJ3V0UM

8.4.2 PPG output operation

The 16-bit timer/event counter can be used for PPG (Programmable Pulse Generator) output by setting 16-bit timer

mode control register 0 (TMC0) and capture/compare control register 0 (CRC0) as shown in Figure 8-9.

The PPG output function outputs a rectangular wave with a cycle specified by the count value set in advance to

16-bit capture/compare register 00 (CR00) and a pulse width specified by the count value set in advance to 16-bit

capture/compare register 01 (CR01).

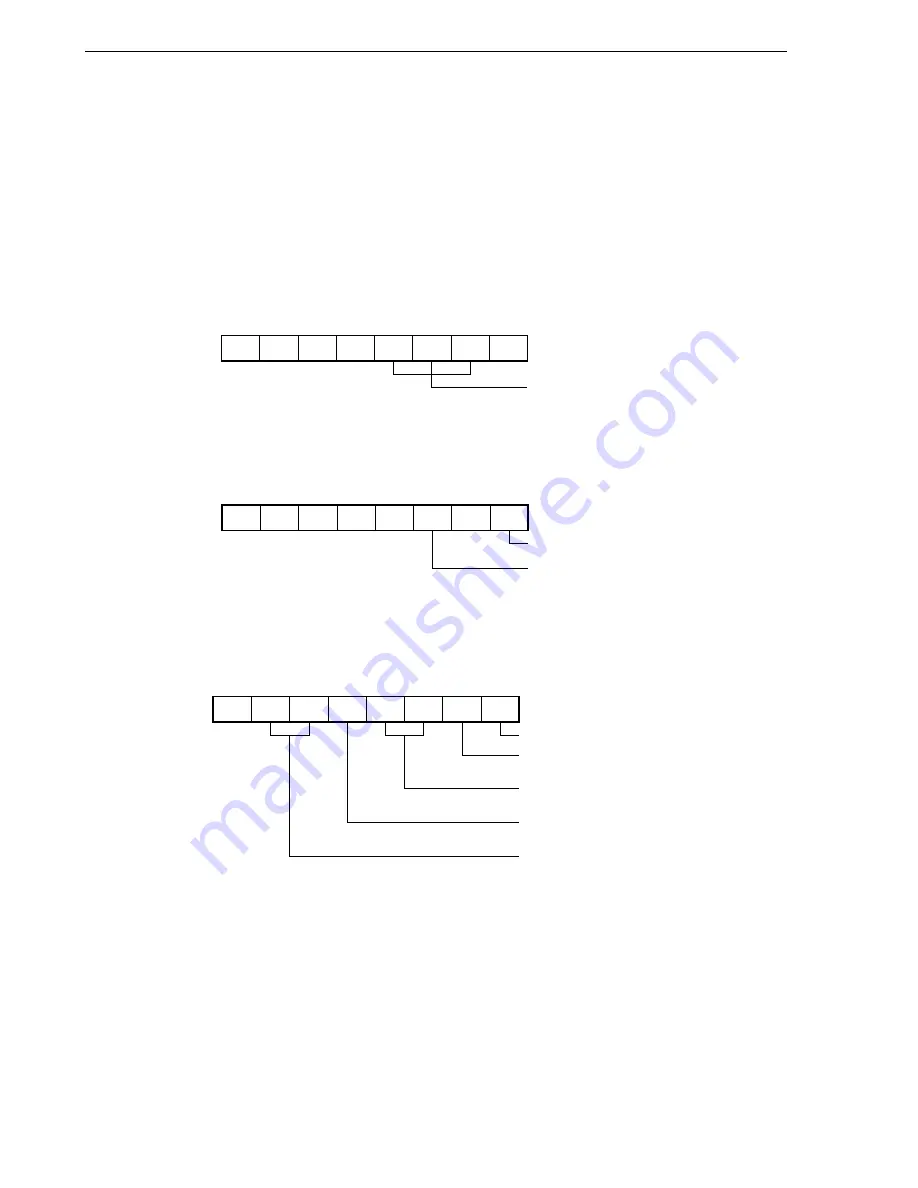

Figure 8-9. Control Register Settings in PPG Output Operation

(a) 16-bit timer mode control register 0 (TMC0)

0

0

0

0

TMC03

1

TMC02

1

TMC01

0

OVF0

0

TMC0

Clears and starts on

match between

TM0 and CR00.

(b) Capture/compare control register 0 (CRC0)

0

0

0

0

0

CRC02

0

CRC01

×

CRC00

0

CRC0

CR00 as compare register

CR01 as compare register

(c) 16-bit timer output control register 0 (TOC0)

0

OSPT

0

OSPE

0

TOC04

1

LVS0

0/1

LVR0

0/1

TOC01

1

TOE0

1

TOC0

Enables TO0 output.

Reverses output on match

between TM0 and CR01.

Disables one-shot pulse output.

Specifies initial value of

TO0 output F/F.

Reverses output on match

between TM0 and CR00.

Remark

×

: don’t care

Caution Make sure that 0000H

≤

CR01

<

CR00

≤

FFFFH is set to CR00 and CR01.