231

CHAPTER 13 A/D CONVERTER

User’s Manual U12697EJ3V0UM

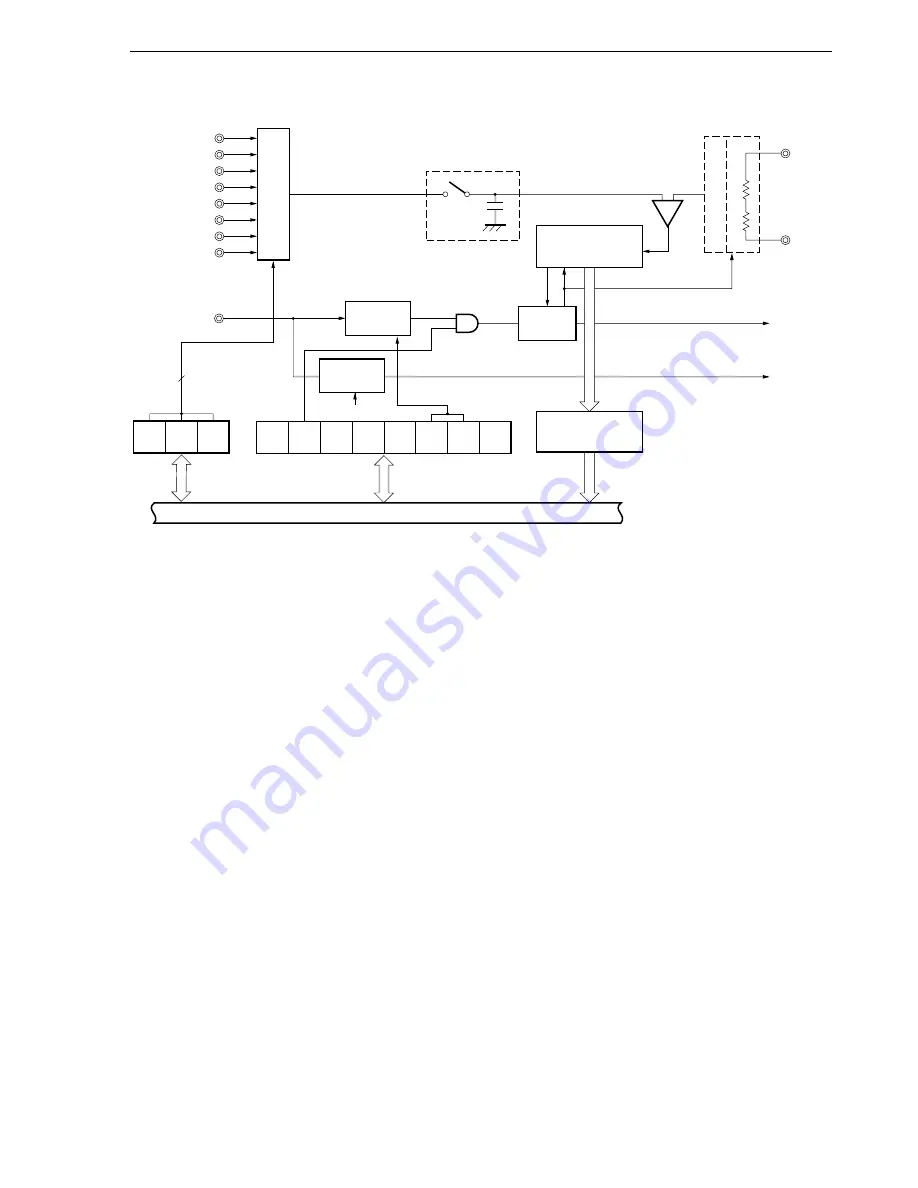

Figure 13-1. Block Diagram of A/D Converter

ANI0

ANI1

ANI2

ANI3

ANI4

ANI5

ANI6

ANI7

Selector

A/D converter

mode register (ADM)

Trigger enable

Sample & hold circuit

3

ADCS

Internal bus

Edge

detector

Edge

detector

Controller

AV

DD

Voltage

comparator

Tap selector

INTAD

INTP3

Successive

approximation

register (SAR)

A/D converter input

selection register (ADIS)

ADIS2 ADIS1 ADIS0

INTP3/P03

TRG FR2 FR1 FR0 EGA1 EGA0 ADCE

A / D conversion

result register

(ADCR)

AV

SS

Note

Note

Valid edge specified with bit 3 (EGP3, EGN3) of external interrupt rising edge/falling edge enable registers

0 (EGP0, EGN0) (Refer to

Figure 21-1 Format of External Interrupt Rising Edge Enable Register 0

(EGP0) and External Interrupt Falling Edge Enable Register 0 (EGN0)

).