295

CHAPTER 18 I

2

C BUS MODE (

µ

PD784225Y SUBSERIES ONLY)

User’s Manual U12697EJ3V0UM

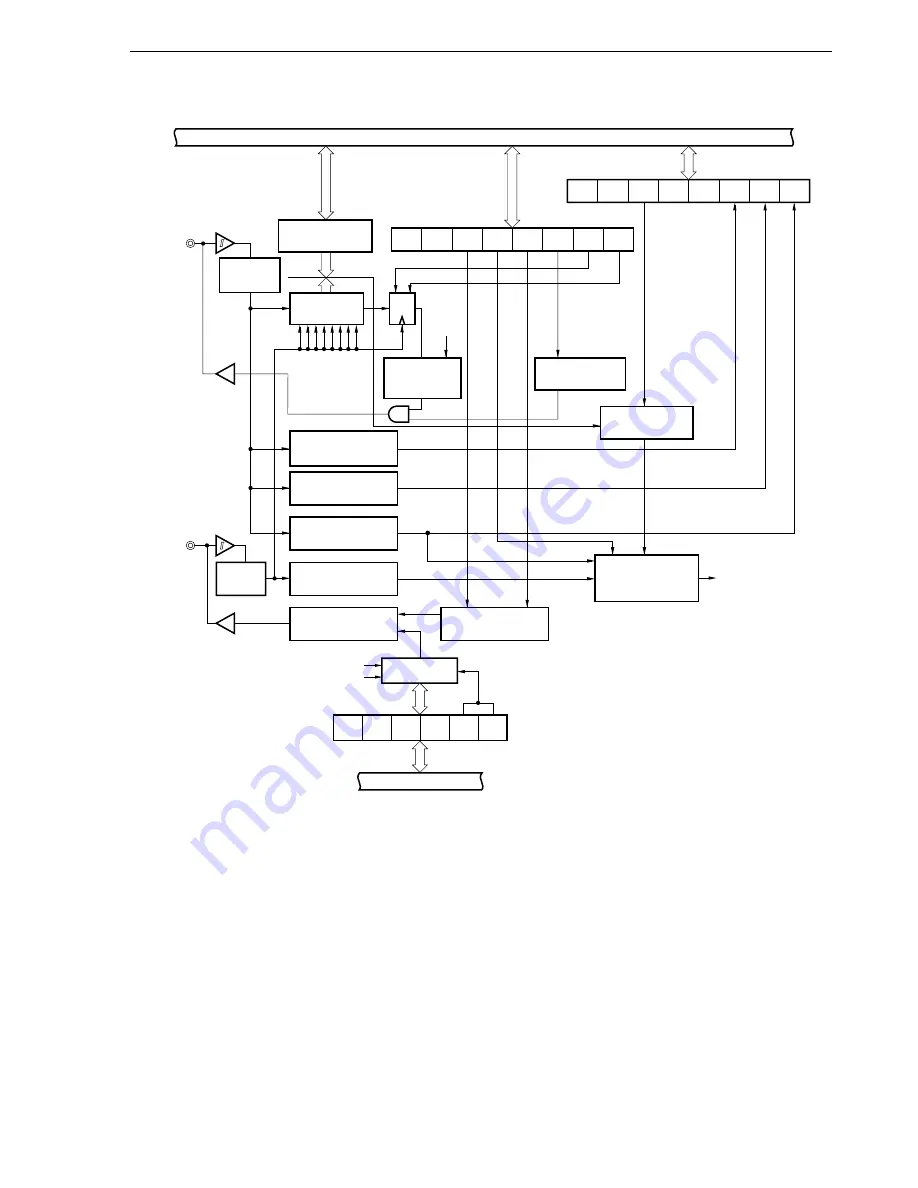

Figure 18-2. Block Diagram of Clocked Serial Interface (I

2

C Bus Mode)

Internal bus

Slave address

register 0 (SVA0)

Noise

eliminator

SDA0

Match

signal

Serial shift

register 0 (IIC0)

Start condition

detector

Stop condition

detector

Interrupt request

signal generator

Serial clock

counter

Serial clock

controller

Serial clock wait

controller

Prescaler mode register 0

for the serial clock (SPRM0)

Noise

eliminator

SCL0

N-ch open-

drain output

Internal bus

f

XX

CL1 CL0

Wake-up

controller

Acknowledge

detector

Acknowledge

detector

Data hold

time correction

circuit

CL1,

CL0

D Q

SO latch

SET

Prescaler

CLEAR

IICE0 LREL0 WREL0 SPIE0 WTIM0 ACKE0 STT0 SPT0

MSTS0 ALD0 EXC0 COI0 TRC0 ACKD0 STD0 SPD0

INTIIC0

I

2

C bus status

register 0 (IICS0)

I

2

C bus control

register 0 (IICC0)

TM2 output

CLD0 DAD0 SMC0 DFC0