300

CHAPTER 18 I

2

C BUS MODE (

µ

PD784225Y SUBSERIES ONLY)

User’s Manual U12697EJ3V0UM

Figure 18-3. Format of I

2

C Bus Control Register 0 (IICC0) (3/4)

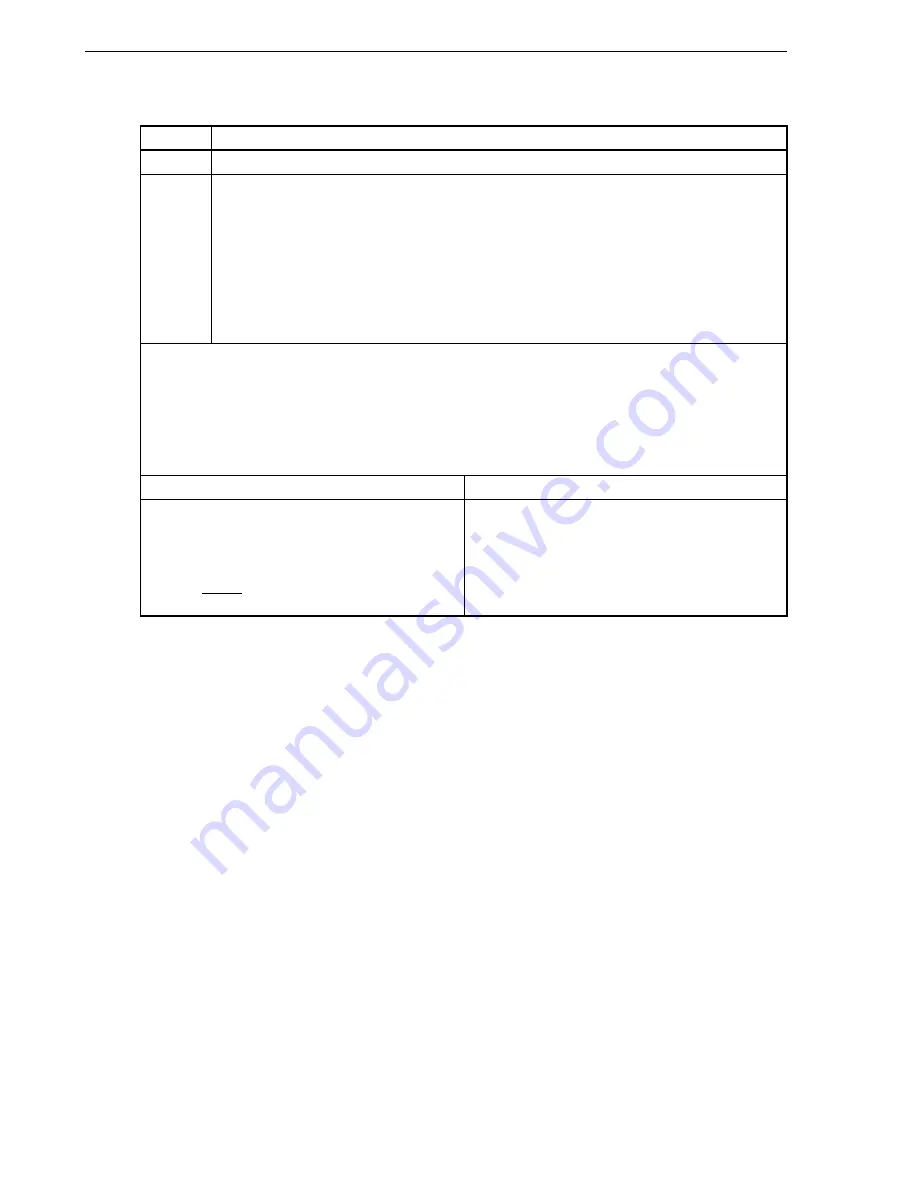

STT0

Start condition trigger

0

The start condition is not generated.

1

• When the bus is released (stop condition):

The start condition is generated (started as the master). The SDA0 line is changed from high to

low, and the start condition is generated. Then, the standard time is guaranteed, and SCL0 goes

low.

• When not participating with the bus:

The trigger functions as the start condition reserved flag. When set, the start condition is auto-

matically generated after the bus is released.

• Wait status (when master)

The wait status is canceled and the restart condition is generated.

Cautions on set timing

•

Master reception:

Setting is prohibited during transfer. STT0 can be set only during the wait period after

ACKE0 = 0 is set and the fact that reception is completed is passed to the slave.

•

Master transmission:

During the ACK0 acknowledge period, the start condition may not be normally gener-

ated. Set STT0 during the wait period.

•

Setting synchronized to SPT0 is prohibited.

•

Resetting between setting STT0 and the generation of the clear condition is prohibited.

Clear condition (STT0 = 0)

Set condition (STT0 = 1)

•

Cleared by an instruction

•

Set by an instruction

•

IICE0 = 0

•

LREL0 = 1

•

When arbitration failed

•

Clear after generating the start condition in the master.

•

When RESET is input