303

CHAPTER 18 I

2

C BUS MODE (

µ

PD784225Y SUBSERIES ONLY)

User’s Manual U12697EJ3V0UM

Figure 18-4. Format of I

2

C Bus Status Register 0 (IICS0) (2/3)

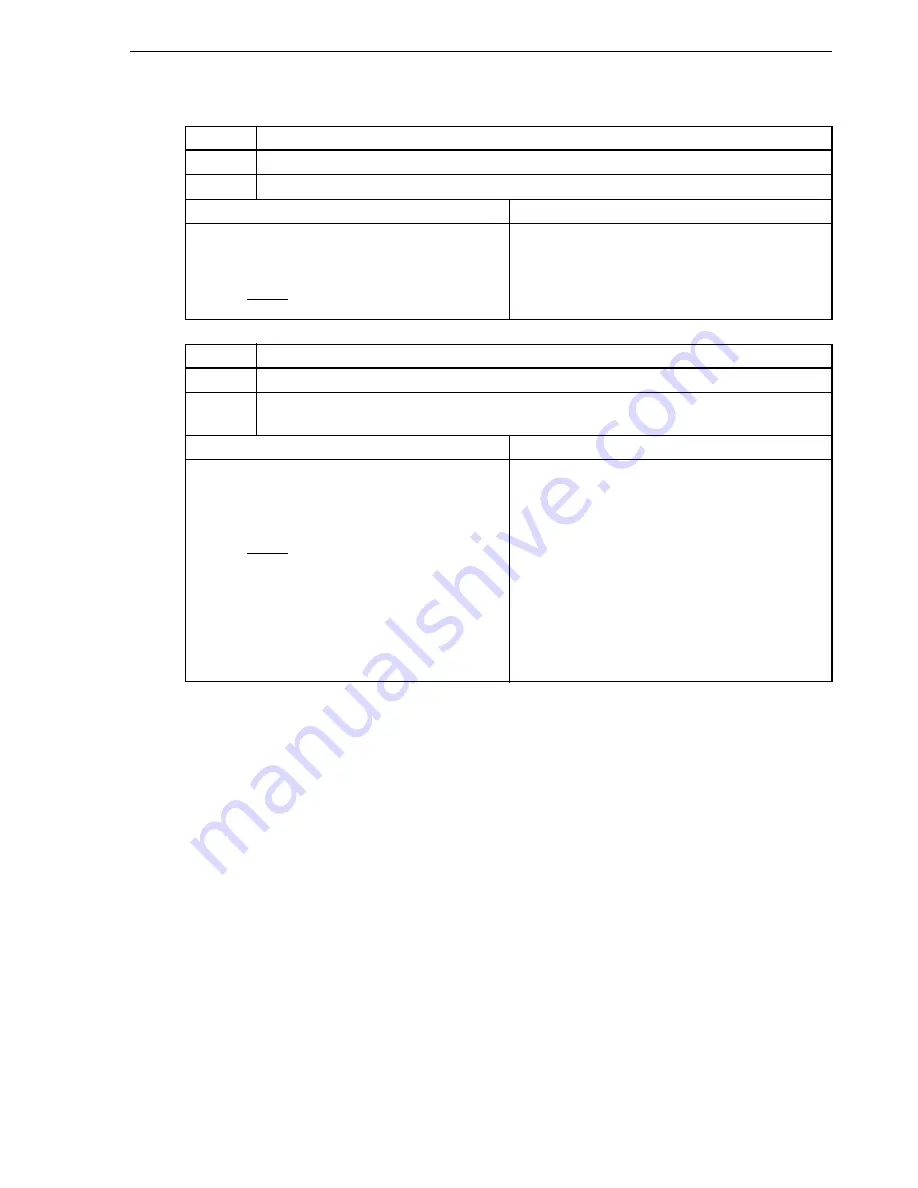

COI0

Address match detection

0

The address does not match.

1

The address matches.

Clear condition (COI0 = 0)

Set condition (COI0 = 1)

•

During start condition detection

•

When the received address matches the base

•

During stop condition detection

address (SVA0) (set at the rising edge of the eighth

•

Cleared by LREL0 = 1

clock)

•

When IICE0 = 1

→

0

•

When RESET is input

TRC0

Transmission/reception state detection

0

Reception state (not the transmission state). The SDA0 line has high impedance.

1

Transmission state. The value in the SO latch can be output to the SDA0 line (valid after the falling

edge of the ninth clock of the first byte)

Clear condition (TRC0 = 0)

Set condition (TRC0 = 1)

•

When the stop condition is detected

In the master

•

Cleared by LREL0 = 1

•

When the start condition is generated

•

When IICE0 = 1

→

0

In the slave

•

Cleared by WREL0 = 1

Note

•

When one is input to the LSB of the first byte

•

When ALD0 = 0

→

1

(transfer direction specification bit)

•

When RESET is input

In the master

•

When one is output to the first byte LSB

(transfer direction specification bit)

In the slave

•

When the start condition is detected

When not participating in the communication

Note

If a wait is cancelled by setting bit 5 (WREL0) of I

2

C bus control register 0 (IICC0) at the ninth clock while

bit 3 (TRC0) of I

2

C bus status register 0 (IICS0) is 1, TRC0 is cleared and the SDA0 line becomes high

impedance.