333

CHAPTER 18 I

2

C BUS MODE (

µ

PD784225Y SUBSERIES ONLY)

User’s Manual U12697EJ3V0UM

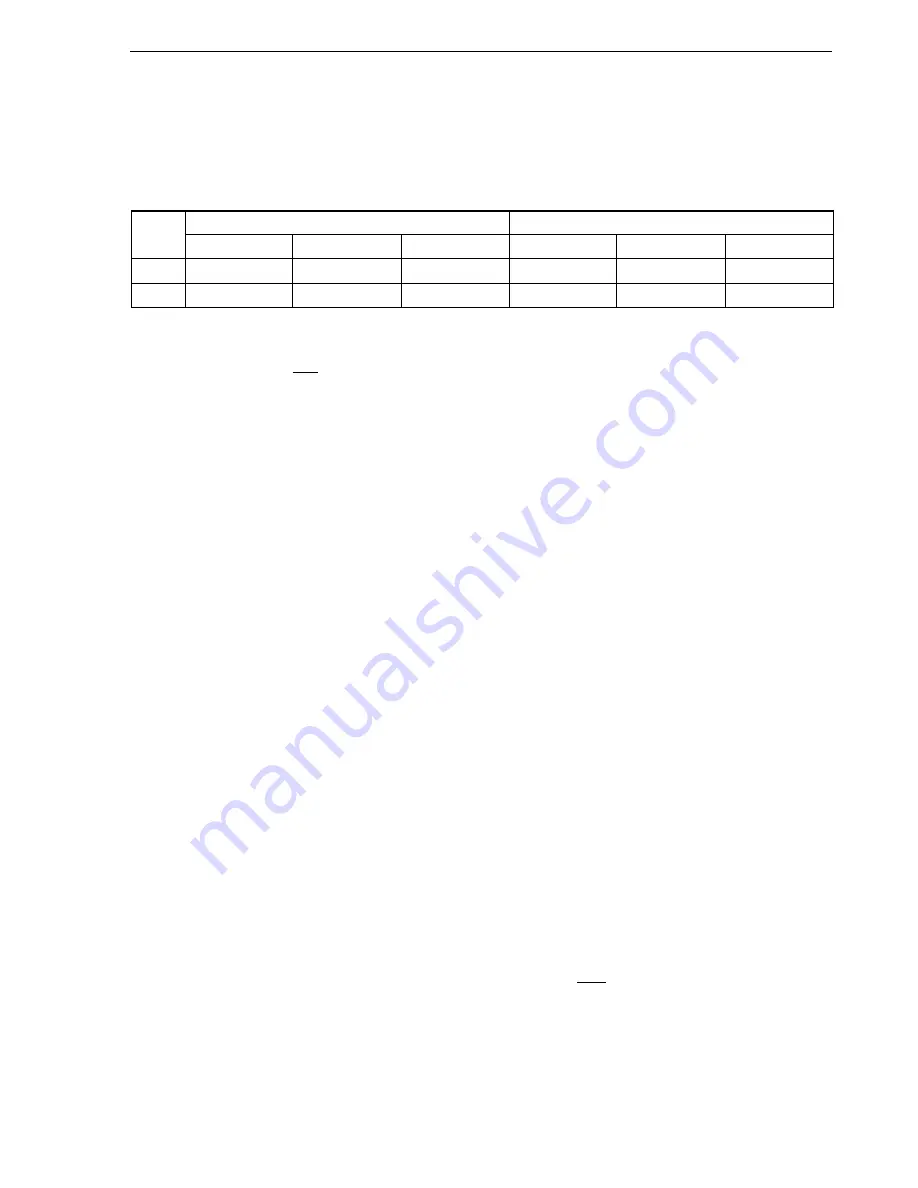

18.5.8 Interrupt request (INTIIC0) generation timing and wait control

By setting the WTIM0 bit in I

2

C bus control register 0 (IICC0), INTIIC0 is generated at the timing shown in Table

18-2 and wait control is performed.

Table 18-2. INTIIC0 Generation Timing and Wait Control

WTIM0

During Slave Operation

During Master Operation

Address

Data Reception

Data Transmission

Address

Data Reception

Data Transmission

0

9

Notes 1, 2

8

Note 2

8

Note 2

9

8

8

1

9

Notes 1, 2

9

Note 2

9

Note 2

9

9

9

Notes 1.

The INTIIC0 signal and wait of the slave are generated on the falling edge of the ninth clock only when

the address set in slave address register 0 (SVA0) matches.

In this case, ACK is output regardless of the ACKE0 setting. The slave that received the extended code

generates INTIIC0 at the falling edge of the eighth clock.

2.

When the address that received SVA0 does not match, INTIIC0 and wait are not generated.

Remark

The numbers in the table indicate the number of clocks in the serial clock. In addition, the interrupt

request and wait control are both synchronized to the falling edge of the serial clock.

(1) When transmitting and receiving an address

•

When the slave is operating:

The interrupt and wait timing are determined regardless of the WTIM0 bit.

•

When the master is operating: The interrupt and wait timing are generated by the falling edge of the ninth

clock regardless of the WTIM0 bit.

(2) When receiving data

•

When the master and slave are operating: The interrupt and wait timing are set by the WTIM0 bit.

(3) When transmitting data

•

When the master and slave are operating: The interrupt and wait timing are set by the WTIM0 bit.

(4) Releasing a wait

The following four methods release a wait.

•

WREL0 = 1 in I

2

C bus control register 0 (IICC0)

•

Writing to serial shift register 0 (IIC0)

•

Setting the start condition (STT0 = 1 in IICC0)

•

Setting the stop condition (SPT0 = 1 in IICC0)

When eight clock waits are selected (WTIM0 = 0), the output level of ACK must be determined before releasing

the wait.

(5) Stop condition detection

INTIIC0 is generated when the stop condition is detected.