393

CHAPTER 22 INTERRUPT FUNCTIONS

User’s Manual U12697EJ3V0UM

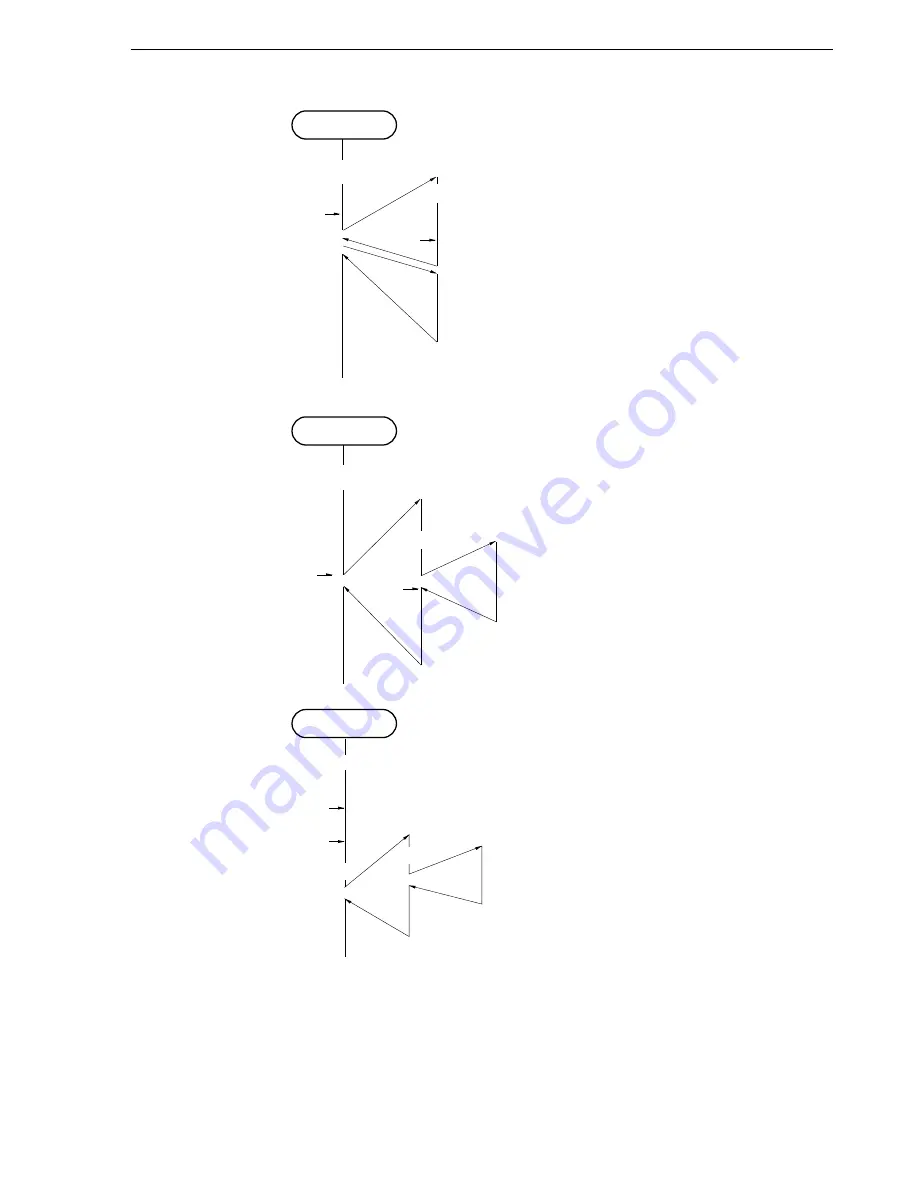

Figure 22-16. Differences in Level 3 Interrupt Acknowledgment According to IMC Register Setting

Notes 1.

Low default priority

2.

High default priority

Remarks 1.

“a” to “f” in the figure above are arbitrary names used to differentiate between the interrupt requests

and macro service requests.

2.

High/low default priorities in the figure indicate the relative priority levels of the two interrupt

requests.

Main routine

EI

EI

Interrupt request a

(Level 3)

Interrupt

request b

(Level 3)

a servicing

b servicing

Interrupt request c

(Level 3)

Interrupt

request d

(Level 3)

c servicing

d servicing

Interrupt request e

Note 1

(Level 3)

Interrupt request f

Note 2

(Level 3)

f servicing

e servicing

IMC

←

80H

EI

Main routine

IMC

←

00H

EI

Main routine

EI

EI

The PRSL bit of the IMC is set to 1, and

nesting between level 3 interrupts is

disabled.

Even though interrupts are enabled, interrupt

request b is held pending since it has the

same priority as interrupt request a.

The PRSL bit of the IMC is set to 0, so that a

level 3 interrupt is acknowledged even during

level 3 interrupt servicing (nesting is

possible).

Since level 3 interrupt request c is being

serviced in the interrupt enabled state and

PRSL = 0, interrupt request d, which is also

level 3, is acknowledged.

As interrupt request 3 and f are both of the

same level, the one with the higher default

priority, f, is acknowledged first.

When the interrupt enabled state is set

during servicing of interrupt request f,

pending interrupt request e is acknowledged

since PRSL = 0.

IMC

←

00H