70

CHAPTER 3 CPU ARCHITECTURE

User’s Manual U12697EJ3V0UM

3.6

µ

PD78F4225 Memory Mapping

The

µ

PD78F4225 has a 128 KB flash memory and 4,352-byte internal RAM.

The

µ

PD78F4225 has a function (memory size switching function) so that a part of the internal memory is not used

by the software.

The memory size is switched by the internal memory size switching register (IMS).

Based on the IMS setting, the memory mapping can be the same memory mapping as the mask ROM versions

with different internal memories (ROM, RAM).

IMS can only be written by an 8-bit memory manipulation instruction.

RESET input sets IMS to FFH.

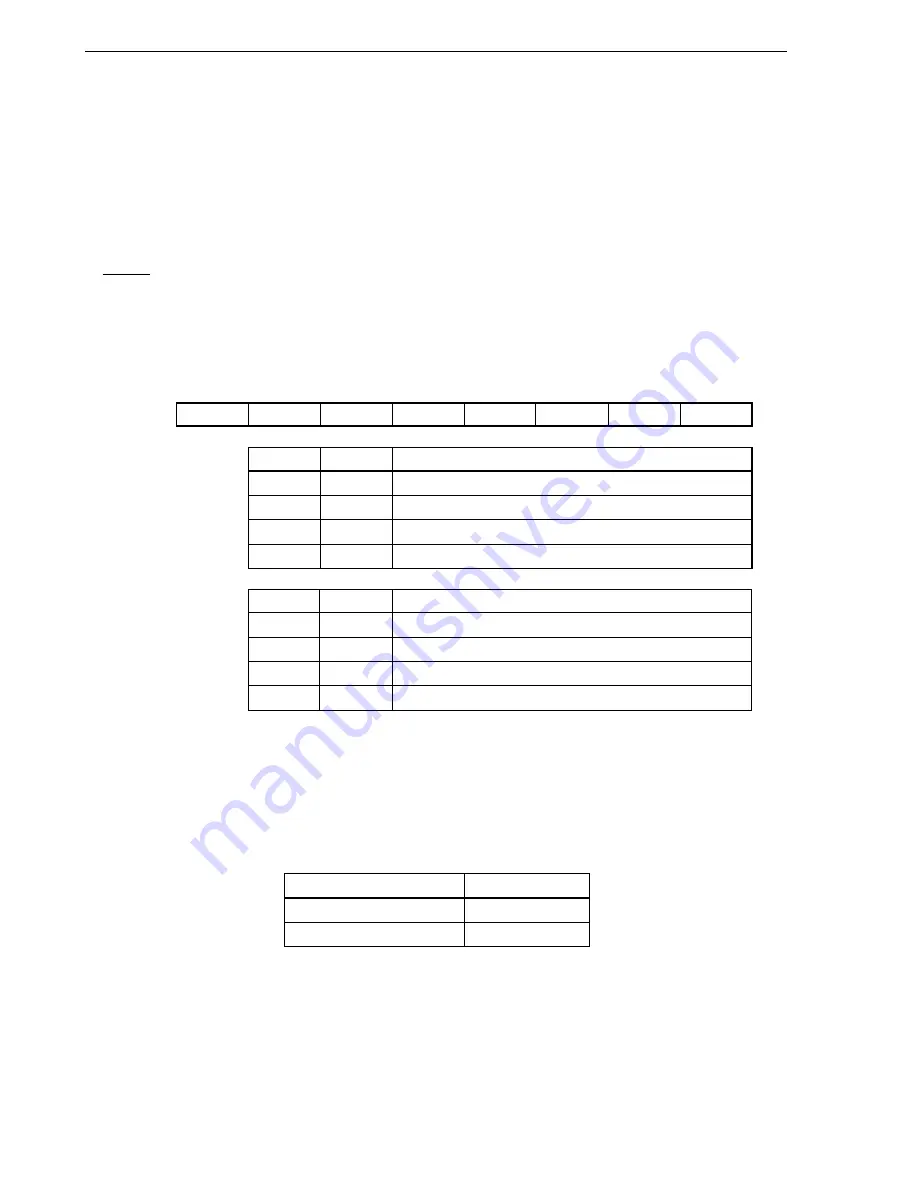

Figure 3-4. Format of Internal Memory Size Switching Register (IMS)

Address: 0FFFCH After reset: FFH W

Symbol

7

6

5

4

3

2

1

0

IMS

1

1

ROM1

ROM0

1

1

RAM1

RAM0

ROM1

ROM0

Internal ROM capacity selections

0

0

48 KB

0

1

64 KB

1

0

96 KB

1

1

128 KB

RAM1

RAM0

Internal RAM capacity selections

0

0

1,536 bytes

0

1

2,304 bytes

1

0

3,072 bytes

1

1

3,840 bytes

Caution Mask ROM versions (

µ

PD784224, 784225) do not have an IMS. Even if a write instructio is

executed to IMS in mask ROM versions, the instruction will be invalid.

Table 3-3 shows the IMS settings that have the same memory map as the mask ROM versions.

Table 3-3. Settings of Internal Memory Size Switching Register (IMS)

Target Mask ROM Versions

IMS Settings

µ

PD784224

EEH

µ

PD784225

FFH