80

CHAPTER 3 CPU ARCHITECTURE

User’s Manual U12697EJ3V0UM

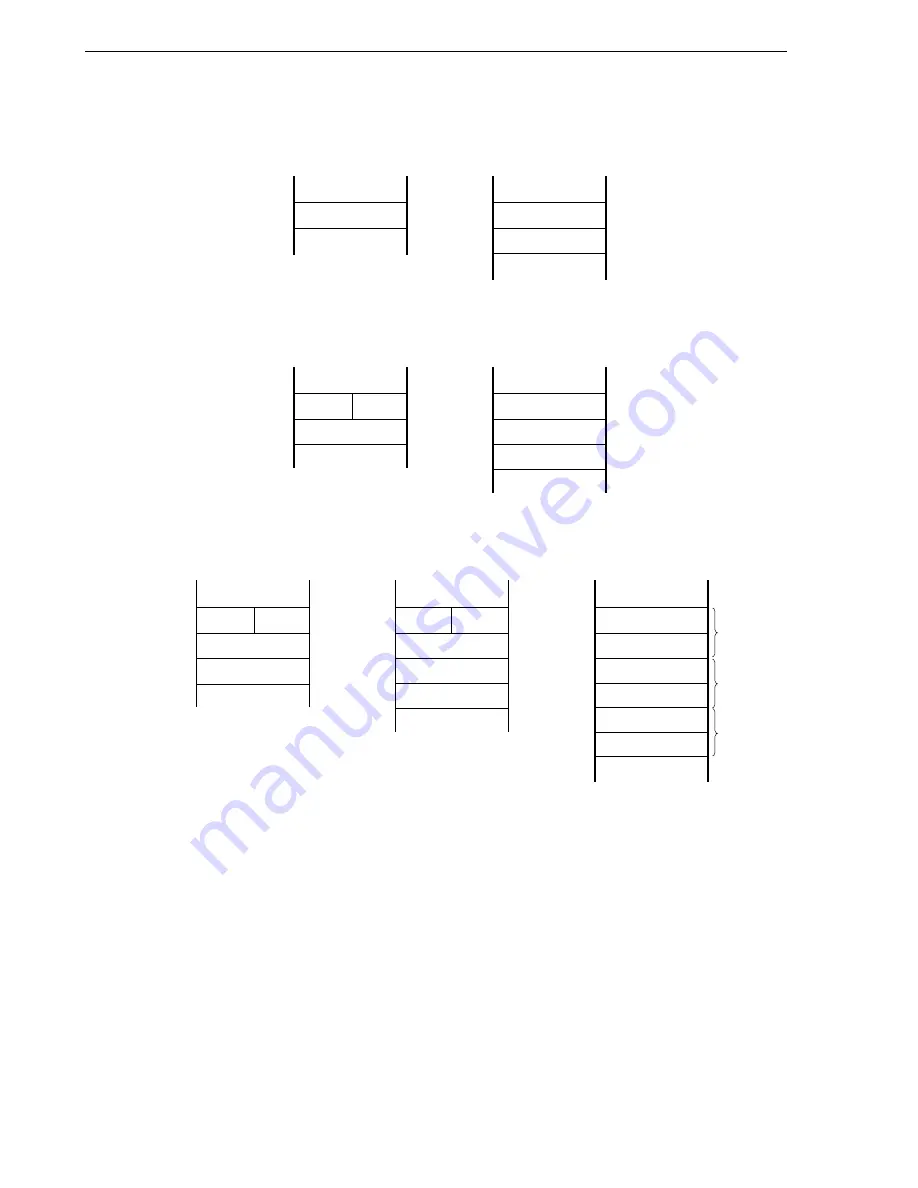

Figure 3-9. Data Restored from the Stack

POP sfr instruction

Stack

POP sfrp instruction

Stack

SP+1

↑

SP

➡

SP

←

SP+1

SP+1

↑

SP

➡

SP

←

SP+2

Higher byte

Lower byte

POP PSW instruction

Stack

POP rg instruction

Stack

↑

SP+1

↑

SP

➡

SP

←

SP+2

SP+2

↑

SP+1

↑

SP

➡

SP

←

SP+3

Higher byte

Middle byte

Lower byte

PSWH

7

to

PSWH

4

PSWH

7

to

PSWH

4

PSWL

—

Note

RET instruction

Stack

RETI, RETB instructions

Stack

SP+2

↑

SP+1

↑

SP

➡

SP

←

SP+3

SP+3

↑

SP+2

↑

SP+1

↑

SP

➡

SP

←

SP+4

PSWL

PC15 to PC8

PC7 to PC0

PC15 to PC8

PC7 to PC0

PC19 to PC16

PC19 to PC16

—

Note

POP post, POPU post instructions

(for POP AX, RP2, RP3)

Stack

SP+5

↑

SP+4

↑

SP+3

↑

SP+2

↑

SP+1

↑

SP

➡

SP

←

SP+6

R6

R7

RP3

R5

R4

A

X

RP2

AX

Note

This 4-bit data is ignored.