96

CHAPTER 4 CLOCK GENERATOR

User’s Manual U12697EJ3V0UM

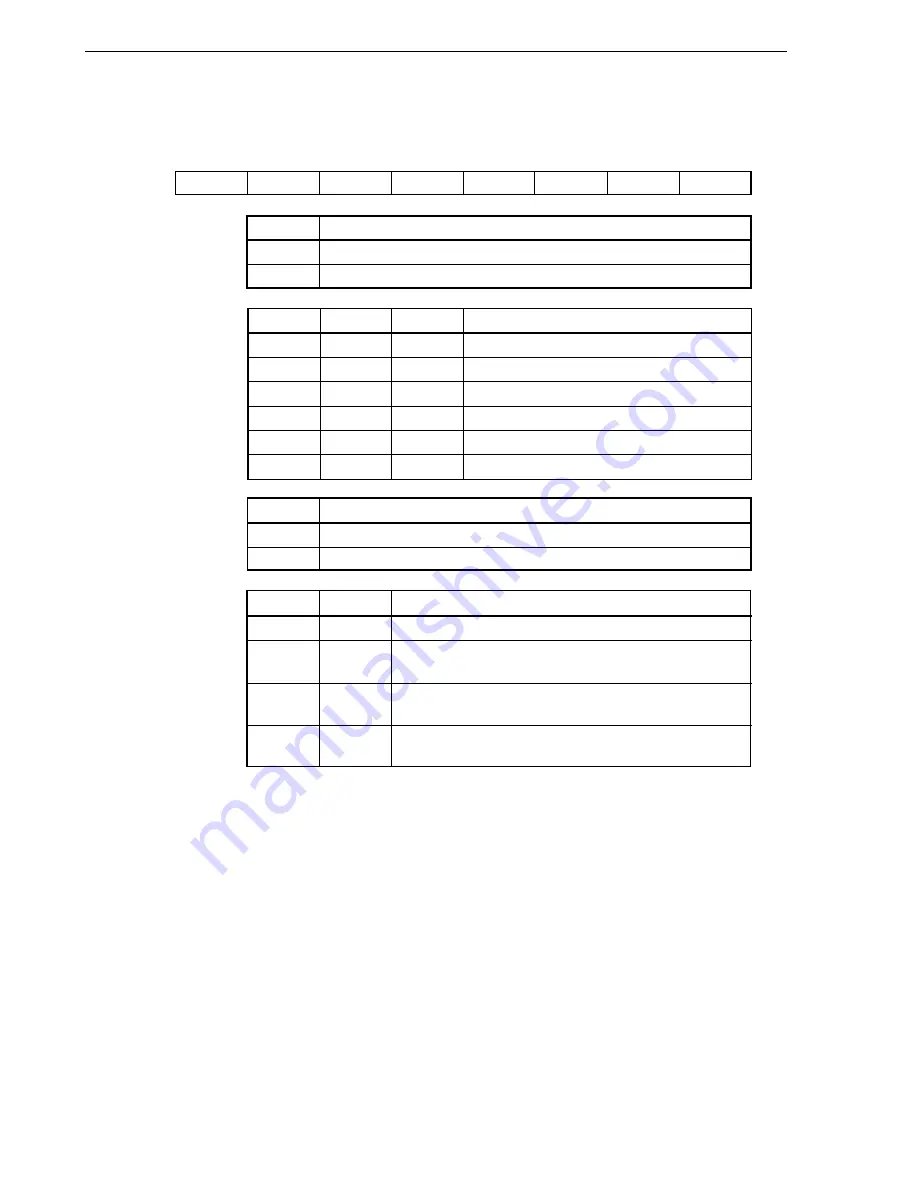

Figure 4-2. Format of Standby Control Register (STBC)

Address: 0FFC0H After reset: 30H R/W

Symbol

7

6

5

4

3

2

1

0

STBC

SBK

CK2

CK1

CK0

0

MCK

STP

HLT

SBK

Subsystem clock oscillation control

0

Use oscillator (Internal feedback resistor is used.)

1

Stop oscillator (Internal feedback resistor is not used.)

CK2

CK1

CK0

CPU clock selection

0

0

0

f

XX

0

0

1

f

XX

/2

0

1

0

f

XX

/4

0

1

1

f

XX

/8

1

1

1

f

XT

(Recommendation)

1

—

—

f

XT

MCK

Main system clock oscillation control

0

Use oscillator (Internal feedback resistor is used.)

1

Stop oscillator (Internal feedback resistor is not used.)

STP

HLT

Operation specification flag

0

0

Normal operation mode

0

1

HALT mode (Automatically cleared upon cancellation of

HALT mode)

1

0

STOP mode (Automatically cleared upon cancellation of

STOP mode)

1

1

IDLE mode (Automatically cleared upon cancellation of

IDLE mode)

Cautions

1. When using the STOP mode during external clock input, make sure to set to 1 the EXTC

bit of the oscillation stabilization time specification register (OSTS) before setting the

STOP mode. If the STOP mode is used during external clock input when the EXTC bit

of OSTS has been cleared (0), the

µ

PD784225 may be damaged or its reliability may be

impaired.

When setting to 1 the EXTC bit of OSTS, the clock with the opposite phase of the clock

input to the X1 pin must be input to the X2 pin.

2. Perform the NOP instruction three times after a standby instruction (after standby

release). Otherwise if contention arises between a standby instruction execution and

an interrupt request, the standby instruction is not performed and the interrupt erquest

is accepted after the execution of several instructions. The instructions executed before

the interrupt request is accepted are instructions whose execution is started within 6

clocks maximum following execution of the standby instruction.