81

Chapter 2

Pin Functions

User’s Manual U16580EE3V1UD00

2.5 Noise

Suppression

The V850E/PH2 has a digital or analog delay circuits for noise suppression on all edge sensitive inputs.

The digital delay circuit suppresses input pulses shorter than the internally generated edge detection

signal to assure the hold time for these signals. The noise suppression is only effective on alternate pin

functions, and it is not effective when the port input function is selected.

Note:

Not available on

μ

PD70F3447

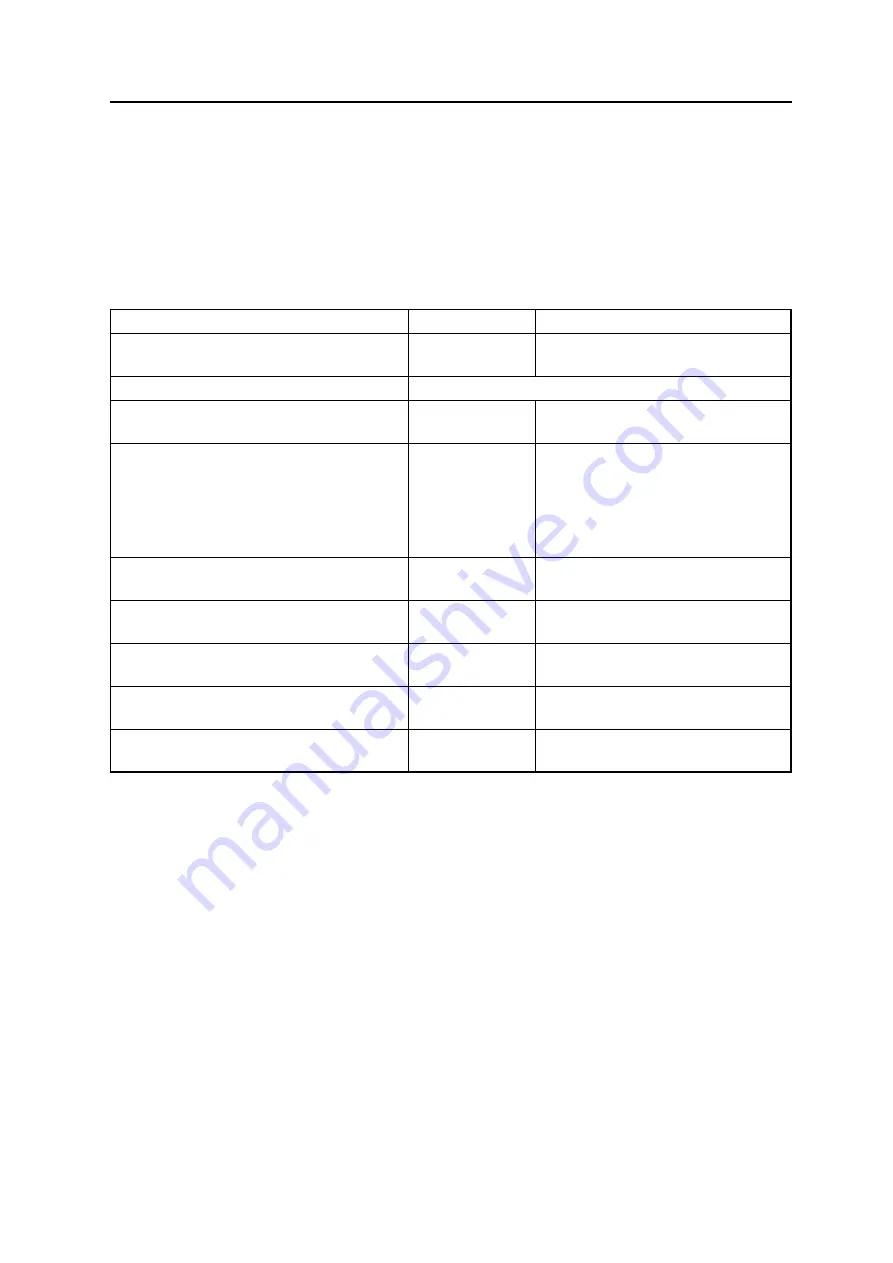

Table 2-5:

Noise Suppression Timing

Pin Function

Noise removal time

Clock Source

NMI

4 to 5 clocks

f

XX

/16 or f

XX

/64

(set by NCR0 bit of NRC register)

INTP0, INTP1, ESO0, ESO1

Analog delay (60ns to 200ns)

INTP2 to INTP11, ADTRG0, ADTRG1

4 to 5 clocks

f

XX

/16 or f

XX

/64

(set by NCR1 bit of NRC register)

INTP12,

TICC00

Note

, TICC01

Note

, TCLR0

Note

,

TCUD0

Note

, TIUD0

Note

,

TIT00, TIT01, TIT10, TIT11, TECRT0, TECRT1,

TEVTT0, TEVTT1, TTRGT0, TTRGT1,

TENCT00, TENCT01, TENCT10, TENCT11

4 to 5 clocks

f

XX

/16 or f

XX

/64

(set by NCR2 bit of NRC register)

TIP00, TIP01, TIP10, TIP11,

TEVTP0, TEVTP1, TTRGP0, TTRGP1

4 to 5 clocks

f

XX

/16 or f

XX

/64

(set by NCR3 bit of NRC register)

TIP20, TIP21, TIP30, TIP31,

TEVTP2, TEVTP3, TTRGP2, TTRGP3

4 to 5 clocks

f

XX

/16 or f

XX

/64

(set by NCR4 bit of NRC register)

TIP40, TIP41, TIP50, TIP51,

TEVTP4, TEVTP5, TTRGP4, TTRGP5

4 to 5 clocks

f

XX

/16 or f

XX

/64

(set by NCR5 bit of NRC register)

TIP60, TIP61, TIP70, TIP71,

TEVTP6, TEVTP7, TTRGP6, TTRGP7

4 to 5 clocks

f

XX

/16 or f

XX

/64

(set by NCR6 bit of NRC register)

TIR10 to TIR13, TEVTR1, TTRGR1

4 to 5 clocks

f

XX

/16 or f

XX

/64

(set by NCR7 bit of NRC register)

Summary of Contents for V850E/PH2

Page 6: ...6 Preface User s Manual U16580EE3V1UD00...

Page 16: ...16 User s Manual U16580EE3V1UD00...

Page 28: ...28 User s Manual U16580EE3V1UD00...

Page 32: ...32 User s Manual U16580EE3V1UD00...

Page 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Page 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Page 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Page 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Page 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Page 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Page 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Page 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Page 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Page 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Page 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Page 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Page 1052: ...1052 User s Manual U16580EE3V1UD00...

Page 1053: ......