208

Chapter 6

DMA Functions (DMA Controller)

User’s Manual U16580EE3V1UD00

6.4.3 DMA transfer of serial interfaces

(1)

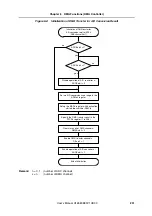

Serial data reception with DMA transfer

The DMAC has two dedicated channels (4 and 5) to support the serial data reception. Each of

both channels can be assigned to a serial interface (CSI30, CSI31

Note

, CSIB0, CSIB1

Note

,

UARTC0, UARTC1). As DMA trigger factor, which requests and starts the DMA transfer, the corre-

sponding interrupt signal at the end of reception is pre-defined (ref. to Table 6-2).

For each DMA trigger the data will be transferred from the corresponding serial reception register

to internal RAM. Depending on the serial interface the transfer data size can be set to 8 or 16 bits

(refer to Table 6-2).

In case of 8 bits transfer data size, the destination address is incremented by 1 for each

occurrence of DMA trigger. When selecting 16 bits transfer data size the destination address must

be even, and is incremented by 2 for each DMA trigger.

When the DMA transfer count of a DMA channel terminates, the DMA transfer is stopped and a

DMA completion interrupt is generated. The maximum DMA transfer count is 256.

Note:

Not available on

μ

PD70F3447.

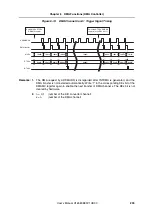

Table 6-2:

DMA Configuration of Serial Data Reception

Serial Interface

DMA Trigger

Factor

Transfer Data

Size

Source

Destination

CSI30

INTC30

8 bits

SIRB0L

Any iRAM address

16 bits

SIRB0

Any even iRAM address

CSI31

Note

INTC31

8 bits

SIRB1L

Any iRAM address

16 bits

SIRB1

Any even iRAM address

CSIB0

INTCB0T

8 bits

CB0RXL

Any iRAM address

16 bits

CB0RX

Any even iRAM address

CSIB1

Note

INTCB1T

8 bits

CB1RXL

Any iRAM address

16 bits

CB1RX

Any even iRAM address

UARTC0

INTUC0T

8 bits

UC0RX

Any iRAM address

16 bits

Setting prohibited

UARTC1

INTUC1T

8 bits

UC1RX

Any iRAM address

16 bits

Setting prohibited

Summary of Contents for V850E/PH2

Page 6: ...6 Preface User s Manual U16580EE3V1UD00...

Page 16: ...16 User s Manual U16580EE3V1UD00...

Page 28: ...28 User s Manual U16580EE3V1UD00...

Page 32: ...32 User s Manual U16580EE3V1UD00...

Page 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Page 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Page 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Page 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Page 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Page 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Page 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Page 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Page 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Page 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Page 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Page 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Page 1052: ...1052 User s Manual U16580EE3V1UD00...

Page 1053: ......