268

Chapter 9

16-Bit Timer/Event Counter P

User’s Manual U16580EE3V1UD00

(4)

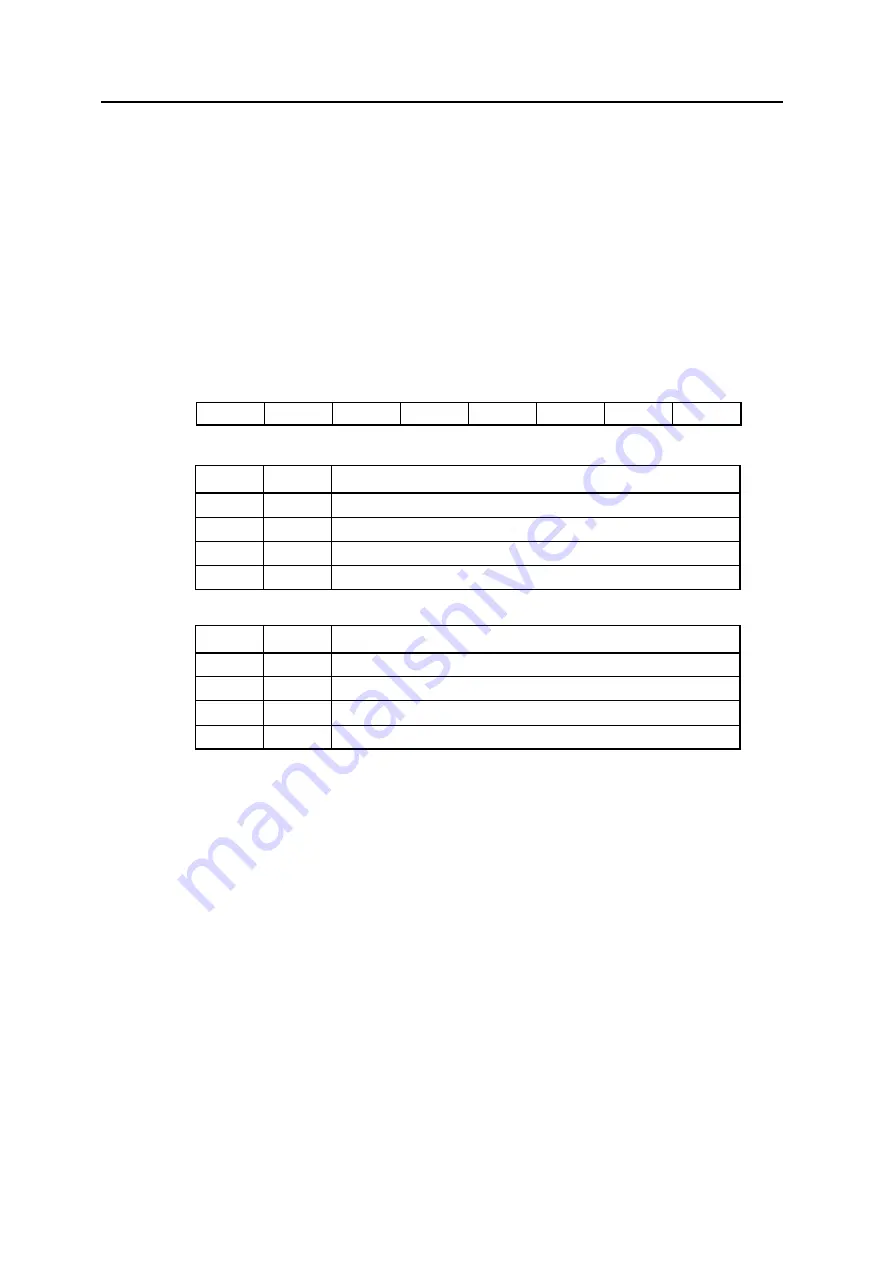

TMPn I/O control register 1 (TPnIOC1)

The TPnIOC1 register is an 8-bit register that controls the valid edge for the external input signals

(TIPn0, TIPn1).

This register can be read or written in 8-bit or 1-bit units.

Reset input clears this register to 00H.

Figure 9-8:

TMPn I/O Control Register 1 (TPnIOC1)

Note:

TIPn0 and TIPn1 input pins are not available for TMP8. These inputs are only connected

internally to capture the interrupt signals INTTT0CC0 and INTT0CC1 of TMT0, or INTCM10

and INTCM11 of TMENC1, specified by the TPIC22 bit of TPIC2 register (ref. to

input control register 2 (TPIC2)

Cautions: 1. Rewrite the TPnIS3 to TPnIS0 bits only when TPnCE = 0. (The same value can be

written when TPnCE = 1.) If rewriting was mistakenly performed, set TPnCE = 0

and then set the bits again.

2. The TPnIS3 to TPnIS0 bits are valid only in the free-running mode and the pulse

width measurement mode. In all other modes, a capture operation is not possible.

Remark:

n = 0 to 8

After reset:

00H

R/W

Address:

TP0IOC1 FFFFF603H, TP1IOC1 FFFFF613H,

TP2IOC1 FFFFF623H, TP3IOC1 FFFFF633H,

TP4IOC1 FFFFF643H, TP5IOC1 FFFFF653H,

TP6IOC1 FFFFF663H, TP7IOC1 FFFFF673H,

TP8IOC1 FFFFF683H

7

6

5

4

3

2

1

0

TPnIOC1

0

0

0

0

TPnIS3

TPnIS2

TPnIS1

TPnIS0

(n = 0 to 8)

TPnIS3

TPnIS2

Capture Input (TIPn1) Valid Edge Setting

Note

0

0

No edge detection (capture operation invalid)

0

1

Rising edge detection

1

0

Falling edge detection

1

1

Both, rising and falling edge detection

TPnIS1

TPnIS0

Capture Input (TIPn0) Valid Edge Setting

Note

0

0

No edge detection (capture operation invalid)

0

1

Rising edge detection

1

0

Falling edge detection

1

1

Both, rising and falling edge detection

Summary of Contents for V850E/PH2

Page 6: ...6 Preface User s Manual U16580EE3V1UD00...

Page 16: ...16 User s Manual U16580EE3V1UD00...

Page 28: ...28 User s Manual U16580EE3V1UD00...

Page 32: ...32 User s Manual U16580EE3V1UD00...

Page 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Page 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Page 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Page 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Page 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Page 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Page 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Page 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Page 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Page 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Page 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Page 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Page 1052: ...1052 User s Manual U16580EE3V1UD00...

Page 1053: ......