474

Chapter 11

16-bit Timer/Event Counter T

User’s Manual U16580EE3V1UD00

(7)

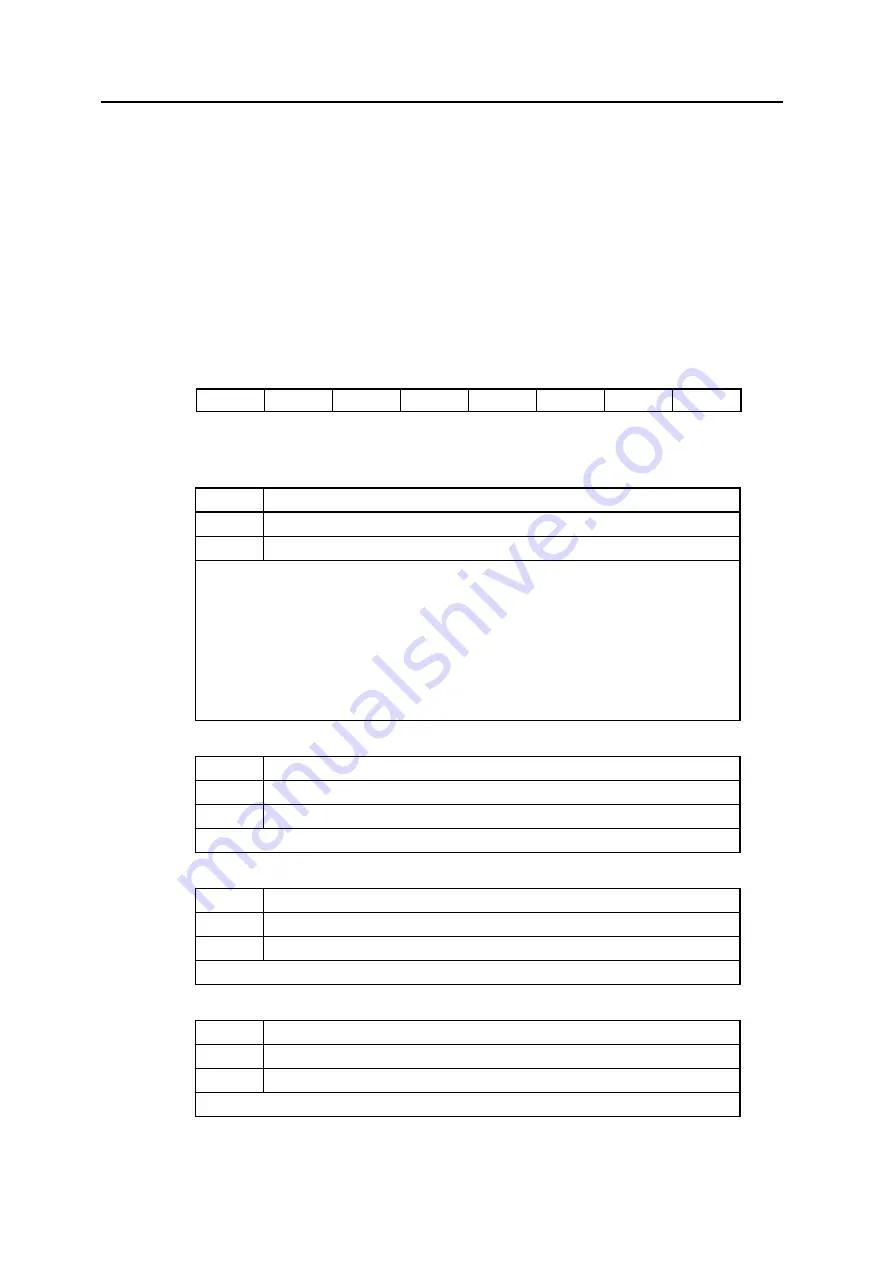

TMTn I/O control register 3 (TTnIOC3)

The TTnIOC3 register is an 8-bit register that controls the valid edge of encoder clear input

(TECRTn pin) and encoder input (TENCTn1 and TENCTn0 pins).

This register can be read and written in 8-bit or 1-bit units.

Reset input clears this register to 00H.

Set the TTnIOC3 register when TTnCE = 0. When TTnCE = 1, write access to the TTnIOC2

register can be performed using the same value.

Figure 11-12:

TMTn I/O Control Register 3 (TTnIOC3) (1/2)

Remark:

n = 0, 1

After reset:

00H

R/W

Address:

TT0IOC3 FFFFF696H,

TT1IOC3 FFFFF6A6H

7

6

5

4

3

2

1

0

TTnIOC3

TTnSCE

TTnZCL

TTnBCL

TTnACL

TTnECS1 TTnECS0 TTnEIS1

TTnEIS0

(n = 0, 1)

TTnSCE

Selects the encoder counter clear method

0

Clear upon detection of edge of TECRTn pin

1

Clear upon match of clear condition level

When TTnSCE = 1, the counter is cleared to 0000H if all the conditions set with bits

TTnZCL, TTnBCL, and TTnACL are matched.

When TTnSCE = 1, the settings of bits TTnECS1 and TTnECS0 are invalid, so no encoder

clear interrupt (INTTTnEC) is output.

When TTnSCE = 0, the settings of bits TTnZCL, TTnBCL, and TTnACL are invalid. The

settings of bits TTnECS1 and TTnECS0 become valid, and the encoder clear interrupt

(INTTTnEC) is output.

Caution:

When TTnSCE = 1, be sure to set bits TTnUDS1, and TTnUDS0 of the

TTnCTL2 register to 10B or 11B.

TTnZCL

Sets the clear level for the Z phase of encoder input (TECRTn pin)

0

Clear condition = Low level

1

Clear condition = High level

Remark:

The TTnZCL bit is valid when TTnSCE = 1.

TTnBCL

Sets the clear level for the B phase of encoder input (TENCTn1 pin)

0

Clear condition = Low level

1

Clear condition = High level

Remark:

The TTnBCL bit is valid when TTnSCE = 1.

TTnACL

Sets the clear level for the A phase of encoder input (TENCTn0 pin)

0

Clear condition = Low level

1

Clear condition = High level

Remark:

The TTnACL bit is valid when TTnSCE = 1.

Summary of Contents for V850E/PH2

Page 6: ...6 Preface User s Manual U16580EE3V1UD00...

Page 16: ...16 User s Manual U16580EE3V1UD00...

Page 28: ...28 User s Manual U16580EE3V1UD00...

Page 32: ...32 User s Manual U16580EE3V1UD00...

Page 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Page 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Page 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Page 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Page 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Page 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Page 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Page 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Page 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Page 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Page 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Page 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Page 1052: ...1052 User s Manual U16580EE3V1UD00...

Page 1053: ......