614

Chapter 15

Asynchronous Serial Interface C (UARTC)

User’s Manual U16580EE3V1UD00

(2)

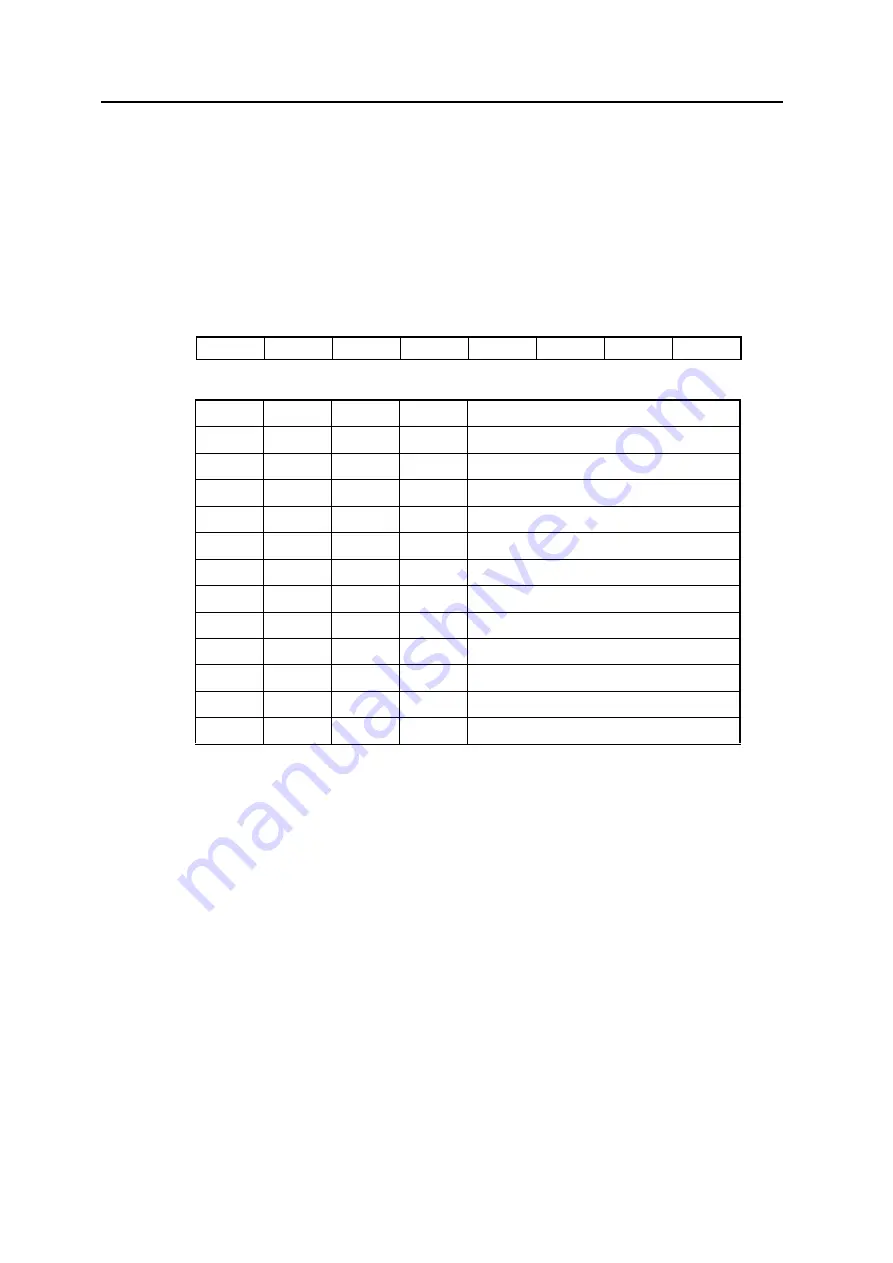

UARTCn control register 1 (UCnCTL1)

The UCnCTL1 register is an 8-bit register that selects the UARTCn base clock

(f

XCLK

)

.

This register can be read or written in 8-bit units.

Reset input clears this register to 00H.

Figure 15-3:

UARTCn Control Register 1 (UCnCTL1)

Remark:

f

XX

: Internal system clock

After reset:

00H

R/W

Address:

UC0CTL1 FFFFFA01H,

UC1CTL1 FFFFFA21H

7

6

5

4

3

2

1

0

UCnCTL1

0

0

0

0

UCnCKS3 UCnCKS2 UCnCKS1 UCnCKS0

(n = 0, 1)

UCnCKS3 UCnCKS2 UCnCKS1 UCnCKS0

Base clock (f

XCLK

) selection

0

0

0

0

f

XX

/2

0

0

0

1

f

XX

/4

0

0

1

0

f

XX

/8

0

0

1

1

f

XX

/16

0

1

0

0

f

XX

/32

0

1

0

1

f

XX

/64

0

1

1

0

f

XX

/128

0

1

1

1

f

XX

/256

1

-

0

0

f

XX

/512

1

-

0

1

f

XX

/1024

1

-

1

0

f

XX

/2048

1

-

1

1

f

XX

/8192

Summary of Contents for V850E/PH2

Page 6: ...6 Preface User s Manual U16580EE3V1UD00...

Page 16: ...16 User s Manual U16580EE3V1UD00...

Page 28: ...28 User s Manual U16580EE3V1UD00...

Page 32: ...32 User s Manual U16580EE3V1UD00...

Page 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Page 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Page 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Page 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Page 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Page 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Page 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Page 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Page 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Page 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Page 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Page 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Page 1052: ...1052 User s Manual U16580EE3V1UD00...

Page 1053: ......