680

Chapter 17

Clocked Serial Interface 3 (CSI3)

User’s Manual U16580EE3V1UD00

17.3 Control

Registers

(1)

Clocked serial interface mode registers 3n (CSIM3n)

The CSIM3n register controls the operation of CSI3n (n = 0, 1).

This registers can be read or written in 8-bit or 1-bit units.

Reset input sets this register to 00H.

Cautions: 1. Writing the TRMDn, DIRn, CSITn, CSWEn, and CSMDn bits is enabled only when

CTXEn bit = 0 and CRXEn bit = 0.

2. To use CSI3n, be sure to set the external pins related to the CSI3n function to

control the mode and set the CSIC3n register. Then set the CSICAEn bit to 1

before setting the other bits.

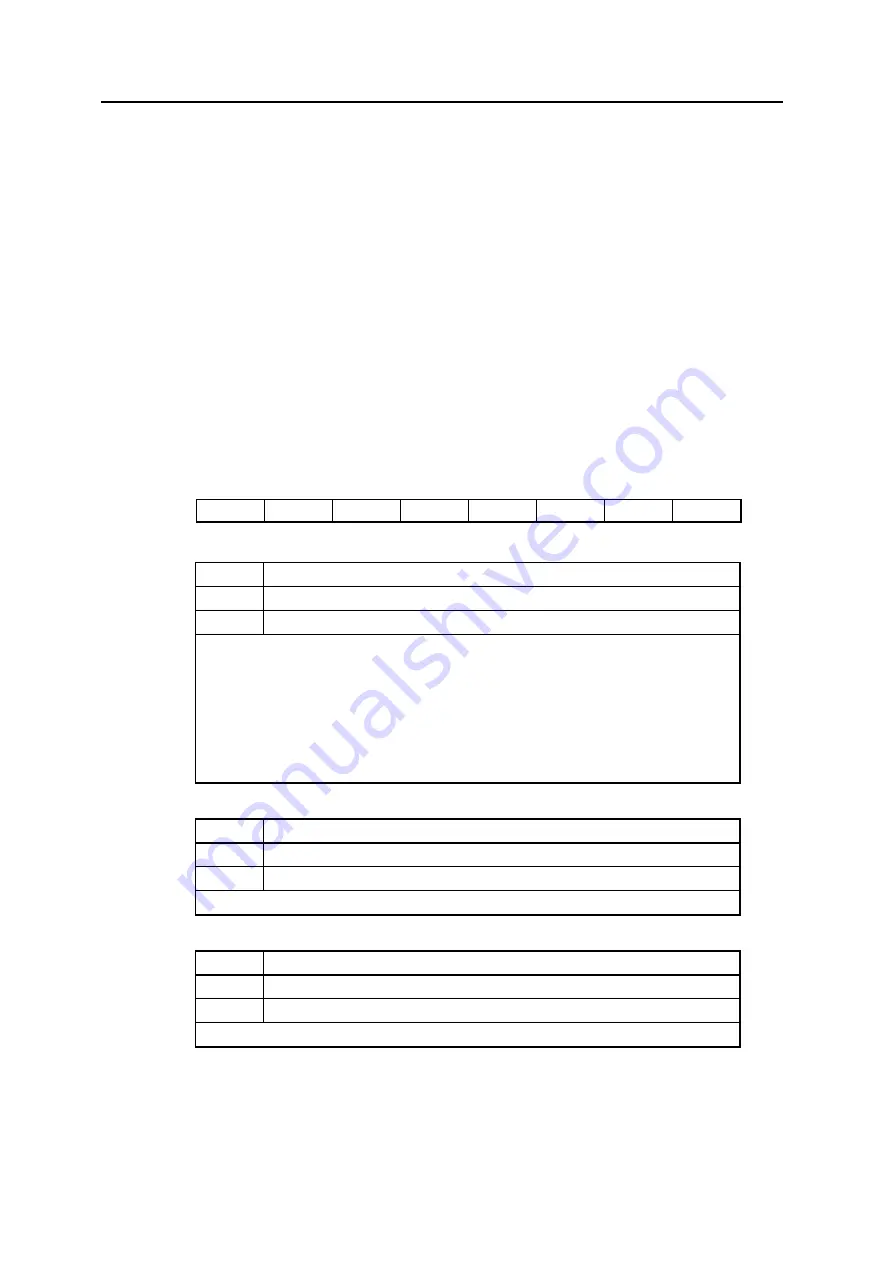

Figure 17-2:

Clocked Serial Interface Mode Register 3n (CSIM3n) (1/2)

Note:

Not available on

µ

PD70F3447

Remark:

μ

PD70F3187:

n = 0, 1

μ

PD70F3447:

n = 0

After reset:

00H

R/W

Address:

CSIM30 FFFFFD40H,

CSIM31 FFFFFD60H

Note

7

6

5

4

3

2

1

0

CSIM3n

CSICAEn

CTXEn

CRXEn

TRMDn

DIRn

CSITn

CSWEn

CSMDn

CSICAEn

CSI3n Operation Clock Control

0

Stops clock supply to CSI3n

1

Supplies clock to CSI3n

Cautions: 1. The CSI3n unit is reset when the CSICAEn bit = 0, and CSI3n is

stopped. To operate CSI3n, first set the CSICAEn bit to 1.

2. When rewriting the CSICAEn bit from 0 to 1 or from 1 to 0,

simultaneously rewriting the bits other than the CSICAEn bit of the

CSIM3n register is prohibited.

When the CSICAEn bit = 0, rewriting the bits other than the CSICAEn

bit of the CSIM3n register, and the SFDB3n, SFDB3nL, and SFA3n

registers is prohibited.

CTXEn

Transmission Operation Enable

0

Disables transmission

1

Enables transmission

Caution:

The CTXEn bit is reset when the CSICAEn bit is cleared to 0.

CRXEn

Reception Operation Enable

0

Disables reception

1

Enables reception

Caution:

The CRXEn bit is reset when the CSICAEn bit is cleared to 0.

Summary of Contents for V850E/PH2

Page 6: ...6 Preface User s Manual U16580EE3V1UD00...

Page 16: ...16 User s Manual U16580EE3V1UD00...

Page 28: ...28 User s Manual U16580EE3V1UD00...

Page 32: ...32 User s Manual U16580EE3V1UD00...

Page 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Page 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Page 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Page 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Page 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Page 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Page 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Page 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Page 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Page 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Page 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Page 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Page 1052: ...1052 User s Manual U16580EE3V1UD00...

Page 1053: ......