814

Chapter 18

AFCAN Controller

User’s Manual U16580EE3V1UD00

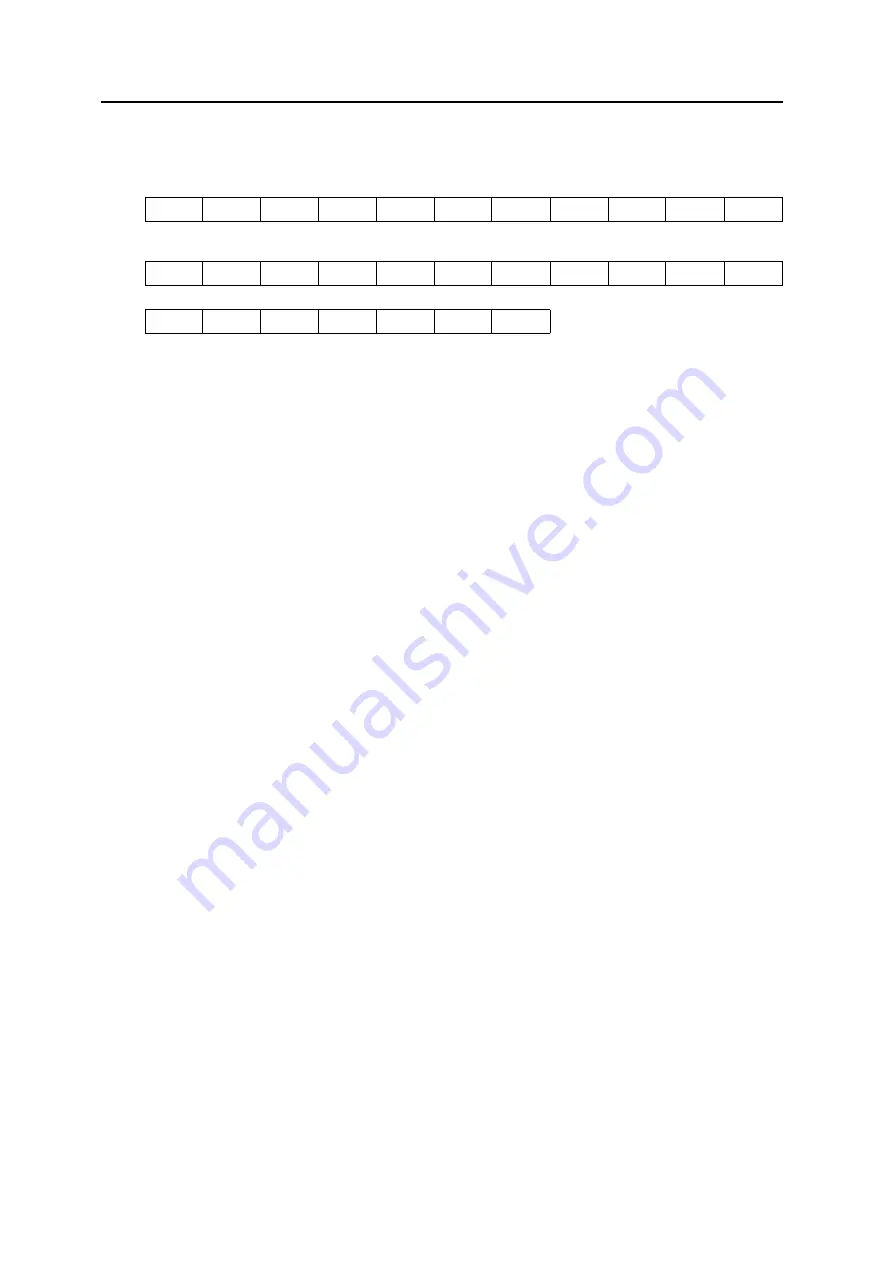

<3> Mask setting for CAN module 1 (mask 1) (Example)

(Using CAN1 address mask 1 registers L and H (C1MASKL1 and C1MASKH1))

1: Not compared (masked)

0: Compared

The CMID27 to CMID24 and CMID22 bits are cleared to 0, and the CMID28, CMID23, and

CMID21 to CMID0 bits are set to 1.

18.9.5 Multi buffer receive block function

The multi buffer receive block (MBRB) function is used to store a block of data in two or more message

buffers sequentially with no CPU interaction, by setting the same ID to two or more message buffers

with the same message buffer type. These message buffers can be allocated anywhere in the message

buffer memory, they do not even have to follow each other adjacently.

Suppose, for example, the same message buffer type is set to 10 message buffers, message buffers 10

to 19, and the same ID is set to each message buffer. If the first message whose ID matches an ID of

the message buffers is received, it is stored in message buffer 10. At this point, the DN bit of message

buffer 10 is set, prohibiting overwriting the message buffer when subsequent messages are received.

When the next message with a matching ID is received, it is received and stored in message buffer 11.

Each time a message with a matching ID is received, it is sequentially (in the ascending order) stored in

message buffers 12, 13, and so on. Even when a data block consisting of multiple messages is

received, the messages can be stored and received without overwriting the previously received match-

ing-ID data.

Whether a data block has been received and stored can be checked by setting the IE bit of the CnMC-

TRLm register of each message buffer. For example, if a data block consists of k messages, k message

buffers are initialized for reception of the data block. The IE bit in message buffers 0 to (k-2) is cleared

to 0 (interrupts disabled), and the IE bit in message buffer k-1 is set to 1 (interrupts enabled). In this

case, a reception completion interrupt occurs when a message has been received and stored in mes-

sage buffer k-1, indicating that MBRB has become full. Alternatively, by clearing the IE bit of message

buffers 0 to (k-3) and setting the IE bit of message buffer k-2, a warning that MBRB is about to overflow

can be issued.

The basic conditions of storing receive data in each message buffer for the MBRB are the same as the

conditions of storing data in a single message buffer.

Caution

1. MBRB can be configured for each of the same message buffer types.

Therefore, even if a message buffer of another MBRB whose ID matches but

whose message buffer type is different has a vacancy, the received

message is not stored in that message buffer, but instead discarded.

2. MBRB does not have a ring buffer structure. Therefore, after a message is stored in the message

buffer having the highest number in the MBRB configuration, a newly received message will not be

stored in the message buffer having the lowest message buffer number.

3. MBRB operates based on the reception and storage conditions; there are no settings dedicated to

MBRB, such as function enable bits. By setting the same message buffer type and ID to two or more

message buffers, MBRB is automatically configured.

4. With MBRB, “matching ID” means “matching ID after mask”. Even if the ID set to each message

CMID2

8

CMID2

7

CMID2

6

CMID2

5

CMID2

4

CMID2

3

CMID2

2

CMID2

1

CMID2

0

CMID1

9

CMID1

8

1

0

0

0

0

1

0

1

1

1

1

CMID1

7

CMID1

6

CMID1

5

CMID1

4

CMID1

3

CMID1

2

CMID1

1

CMID1

0

CMID9

CMID8

CMID7

1

1

1

1

1

1

1

1

1

1

1

CMID6

CMID5

CMID4

CMID3

CMID2

CMID1

CMID0

1

1

1

1

1

1

1

Summary of Contents for V850E/PH2

Page 6: ...6 Preface User s Manual U16580EE3V1UD00...

Page 16: ...16 User s Manual U16580EE3V1UD00...

Page 28: ...28 User s Manual U16580EE3V1UD00...

Page 32: ...32 User s Manual U16580EE3V1UD00...

Page 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Page 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Page 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Page 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Page 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Page 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Page 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Page 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Page 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Page 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Page 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Page 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Page 1052: ...1052 User s Manual U16580EE3V1UD00...

Page 1053: ......