987

Chapter 24

Flash Memory

User’s Manual U16580EE3V1UD00

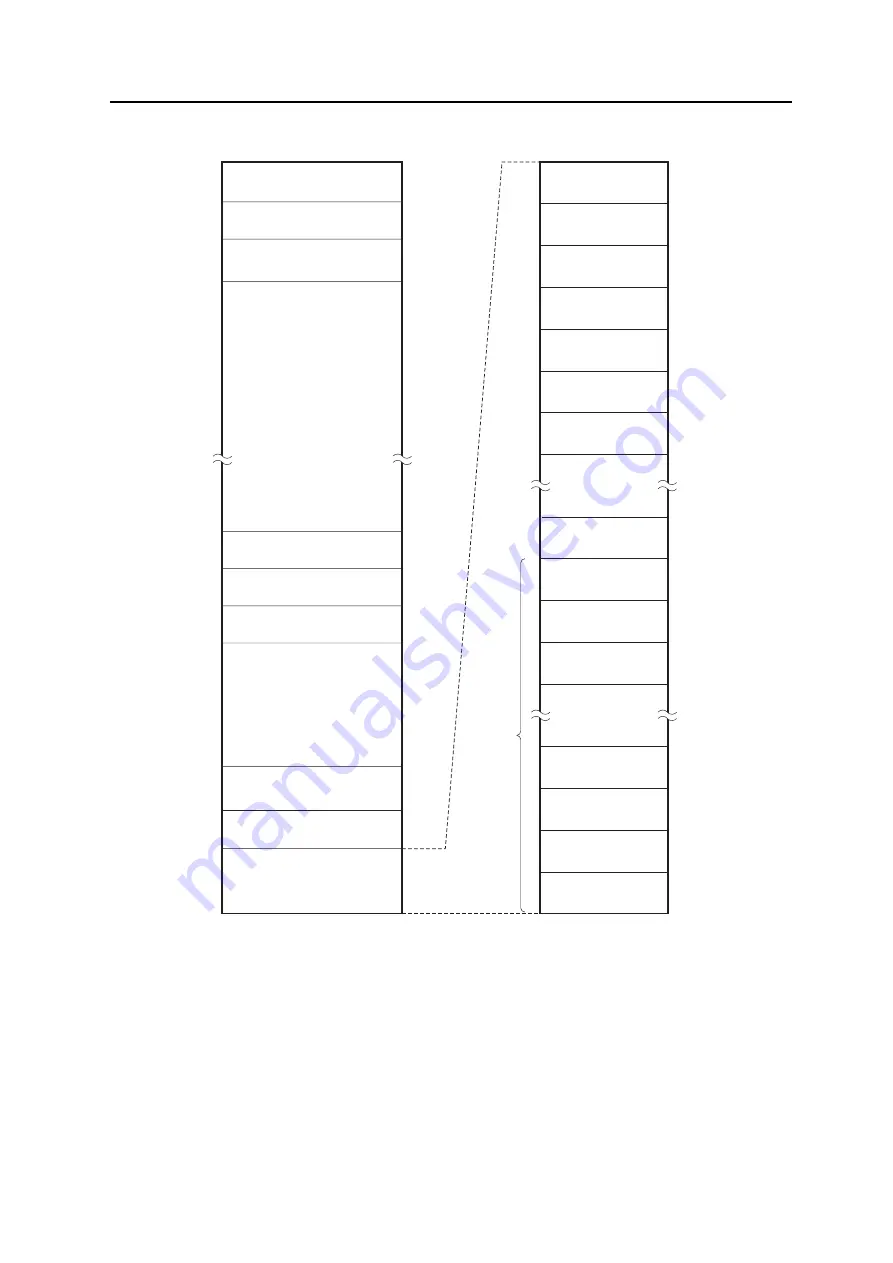

Figure 24-2:

Flash Memory Mapping of

μ

PD70F3447

Note:

Blocks 0 to 15 (64 KB): Boot block cluster

400 0000H

3FF FFFFH

100 0000H

0FF FFFFH

006 0000H

005 FFFFH

020 0000H

01F FFFFH

000 0000H

Extern

a

l memory

a

re

a

(47.9 MB)

U

s

e prohi

b

ited

Extern

a

l memory

a

re

a

(14 MB)

Intern

a

l fl

as

h memory

a

re

a

(

38

4 KB)

U

s

e prohi

b

ited

Note

Intern

a

l RAM

a

re

a

(24 KB)

On-chip peripher

a

l I/O

a

re

a

(4 KB)

Block 14 (4 KB)

Block 15 (4 KB)

Block 16 (4 KB)

Block 1

3

(4 KB)

0000 D000H

0000 CFFFH

0000 E000H

0000 DFFFH

0000 F000H

0000 EFFFH

0001 0000H

0000 FFFFH

0001 1000H

0001 0FFFH

Block 90 (4 KB)

Block

8

9 (4 KB)

Block 91 (4 KB)

Block 92 (4 KB)

Block 9

3

(4 KB)

Block 95 (4 KB)

Block 94 (4 KB)

0005 F000H

0005 EFFFH

0005 E000H

0005 DFFFH

0005 D000H

0005 CFFFH

0005 C000H

0005 BFFFH

0005 B000H

0005 AFFFH

0005 A000H

0005 9FFFH

0005 9000H

0005 8FFFH

0005 FFFFH

Block 0 (4 KB)

Block 1 (4 KB)

Block 2 (4 KB)

Block

3

(4 KB)

0000 2000H

0000 1FFFH

0000 3000H

0000 2FFFH

0000 4000H

0000 3FFFH

0000 1000H

0000 0FFFH

0000 0000H

3FF 0000H

3FE FFFFH

3FF 6000H

3FF 5FFFH

3FF F000H

3FF EFFFH

On-chip peripher

a

l

I/O

a

re

a

mirror

U

s

e prohi

b

ited

U

s

e prohi

b

ited

(

3

6 KB)

Intern

a

l RAM

a

re

a

mirror

FFF FFFFH

FFF 6000H

FFF 5FFFH

FFF EFFFH

FFF F000H

FFE FFFFH

FFF 0000H

Summary of Contents for V850E/PH2

Page 6: ...6 Preface User s Manual U16580EE3V1UD00...

Page 16: ...16 User s Manual U16580EE3V1UD00...

Page 28: ...28 User s Manual U16580EE3V1UD00...

Page 32: ...32 User s Manual U16580EE3V1UD00...

Page 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Page 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Page 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Page 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Page 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Page 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Page 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Page 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Page 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Page 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Page 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Page 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Page 1052: ...1052 User s Manual U16580EE3V1UD00...

Page 1053: ......