N723-EA Hardware User Guide

Chapter 5 Application Interfaces

Copyright © Neoway Technology Co., Ltd. All rights reserved.

28

⚫

Place a bypass capacitor (C4, C5, C6, C7) of low-ESR close to the module to filter out high-

frequency jamming from the power supply.

⚫

Select the capacitors at C8 and C9 based on the specifications and the actual test conditions of

the p-MOSFET since their capacitance may affect the turn-on and off time of the p-MOSFET.

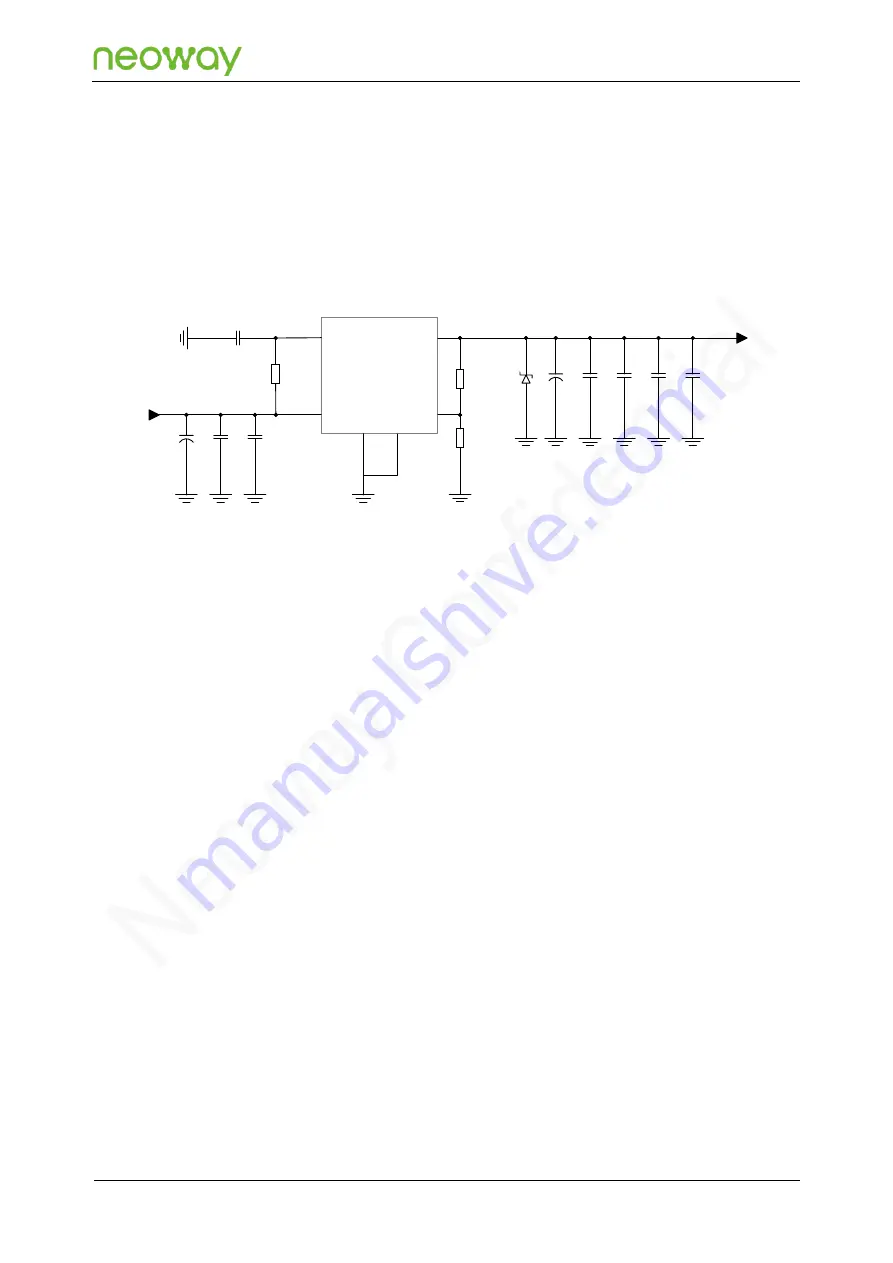

Recommended 4.2V to 5.5 V input design:

Figure 5-4

Recommended design 3

C4

C5

C6

C7

C8

100

μF 10μF 0.1μF 100pF 33pF

D1

100k

Ω±1%

R1

47.5k

Ω±1%

R2

C1

C2

100

μF

EN

VIN

VOUT

ADJ

GND

U1

TVS

0.1

μF

VIN(5.0V)

VBAT

1

2

C3

DNI-33pF

100k

Ω

R2

C9

DNI-0.1

μF

3

5

4

6

PAD

⚫

Design with LDO is more simpler and efficient when the output of power supply is close to the

permissible voltage across VBAT.

⚫

It is recommended to select an LDO that its maximum output current be greater than 2.5 A at U1.

⚫

The TVS diode selected at D1 has a reverse operating voltage (V

RWM

) of 4.5 V, and its peak

power Ppp is 2800 W (tp=8/20 uS). It has the surge protection mechanism. Place the TVS close

to the power input interface to clamp the surge voltage before it enters back-end circuits.

Therefore, the back-end components and the module are protected.

⚫

Place C4 close to the module. A large tantalum electrolytic capacitor (220 μF or 100 μF) or

aluminum electrolytic capacitor (470 μF or 1000 μF) can be selected at C4 to improve the

instantaneous large current freewheeling ability of the power supply. Its withstand voltage should

be larger than 2 times the voltage of the power supply.

⚫

Place a bypass capacitor (C5, C6, C7, C8) of low-ESR close to the module to filter out high-

frequency jamming from the power supply.