© National Instruments

|

1-1

1

Before You Begin

This section contains information you need before developing high-performance embedded

applications using the NI-7931R, NI-7932R, and NI-7935R devices.

Development Requirements

Successful system design with the NI-793xR devices may require knowledge in the following

areas, depending on your application.

•

Real-time programming

•

VHDL code design

•

LabVIEW and LabVIEW FPGA programming

If you are unfamiliar with any of these concepts, refer to the following table for a list of resources

for learning the fundamentals required for NI-793xR development.

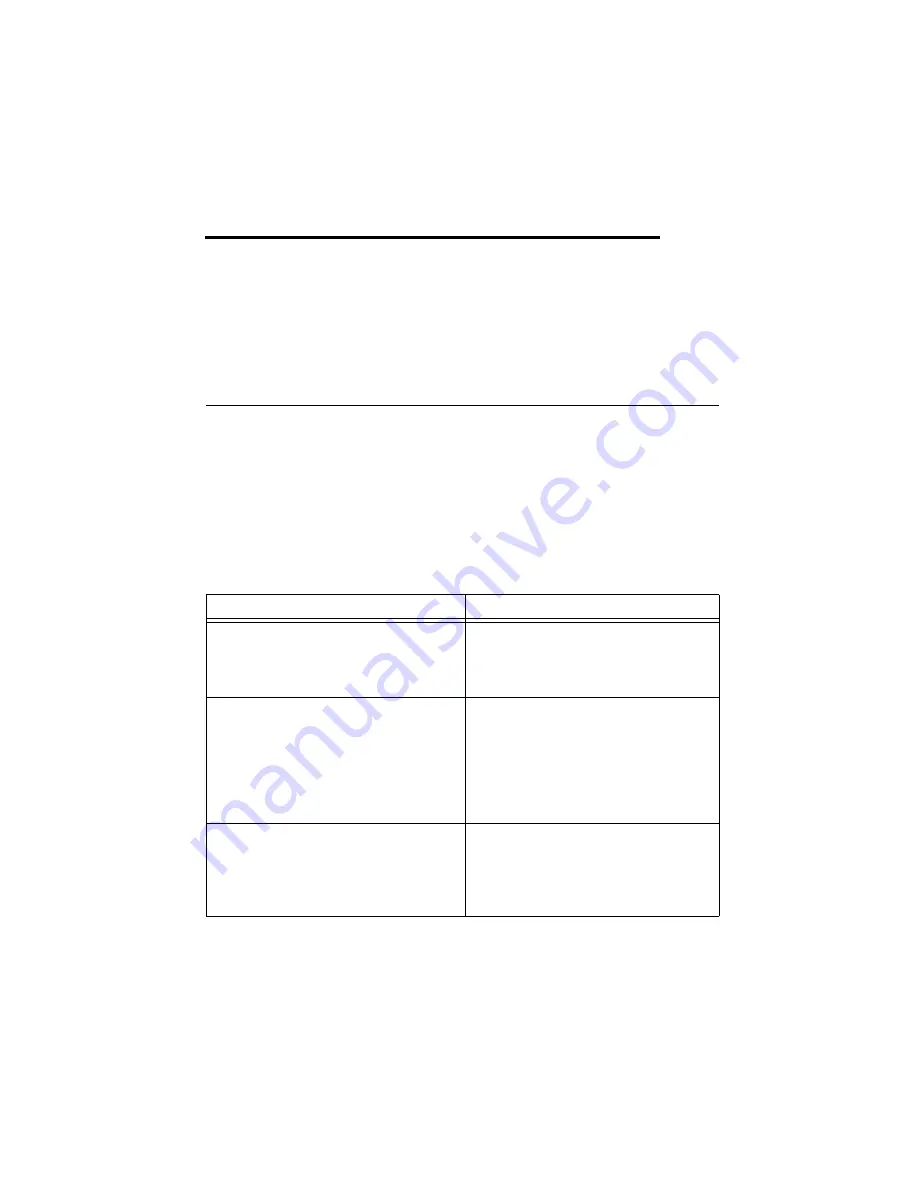

Table 1-1.

Fundamentals Resources

Concept

Resources

Real-time programming

Real-time programming courses are

available at

. You can

also refer to the

LabVIEW Real-Time

Module Help

at

.

VHDL code design

Some VHDL training or experience is

required before implementing custom

protocols with the high-speed serial

transceivers. Do not attempt to develop

Component-Level IP (CLIP) without

VHDL knowledge. Refer to the

FlexRIO

Help

for more information about CLIP.

LabVIEW and LabVIEW FPGA

programming

LabVIEW and LabVIEW FPGA training

are available at

. You

can also refer to the

NI LabVIEW

High-Performance FPGA Developer’s

Guide

, available at