© National Instruments

|

3-3

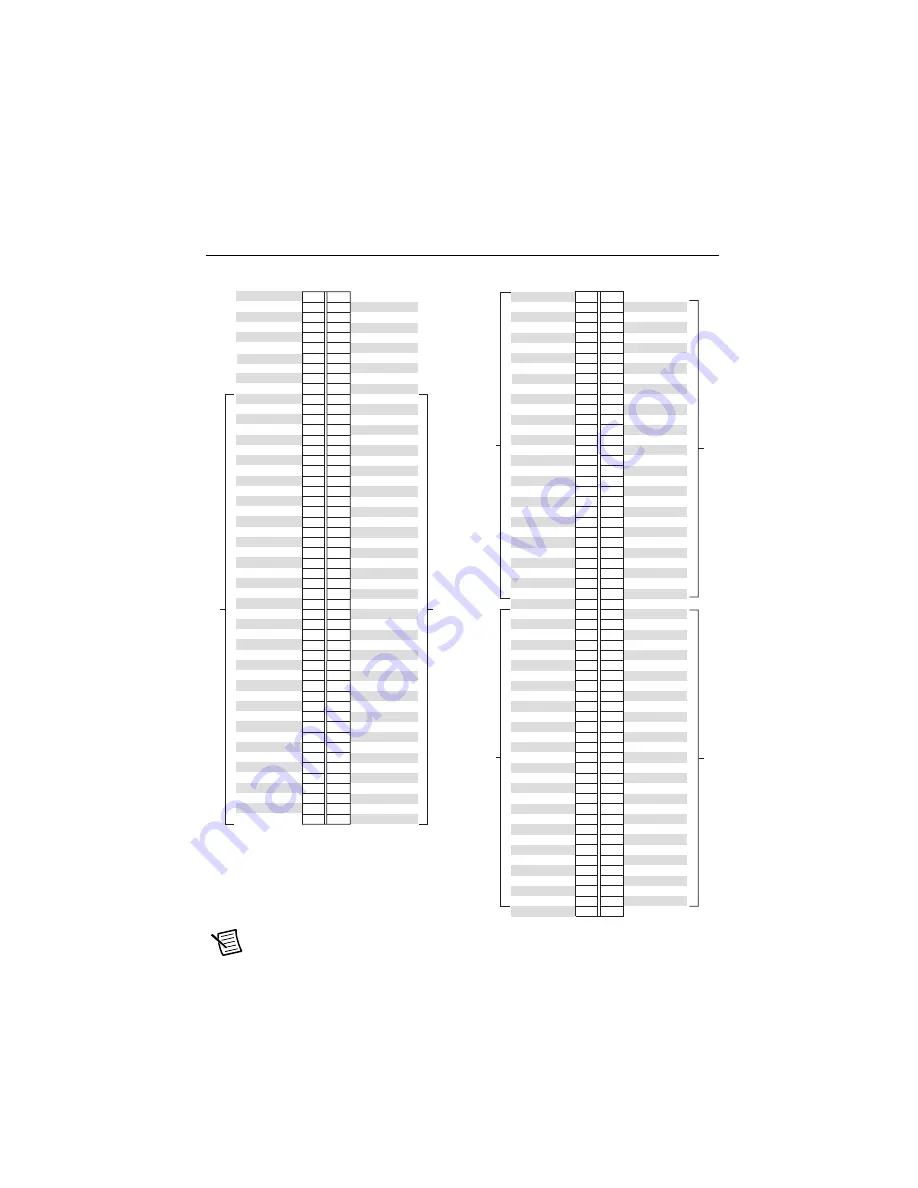

The following figure shows the available signals on the NI-7931R adapter module connector.

Figure 3-3.

NI-7931R FPGA Connector Pinout

Note

Pins S72 and S146 are shorted together.

B

a

nk 1

PCB

Primary Side

+

3

.

3

V

S

CL

TB_Pre

s

ent_n

+12V

Vcco

R

S

VD

GND

IOMod

S

yncClk_n

IOMod

S

yncClk

GND

GPIO_0_n

GPIO_0

GND

GPIO_1_n

GPIO_1

GND

GPIO_CC_2_n

GPIO_CC_2

GND

GPIO_

3

_n

GPIO_

3

GND

GPIO_4_n

GPIO_4

GND

GPIO_5_n

GPIO_5

GND

GPIO_6_n

GPIO_6

GND

GPIO_7_n

GPIO_7

GND

GPIO_

8

_n

GPIO_

8

GND

GPIO_9_n

GPIO_9

GND

GPIO_10_n

GPIO_10

GND

GPIO_11_n

GPIO_11

GND

GPIO_12_n

GPIO_12

GND

GND

GPIO_1

3

_n

GPIO_1

3

P2

P1

S

14

8

S

147

S

146

S

145

S

144

S

14

3

G

3

6

S

142

S

141

G

3

5

S

140

S

1

3

9

G

3

4

S

1

38

S

1

3

7

G

33

S

1

3

6

S

1

3

5

G

3

2

S

1

3

4

S

1

33

G

3

1

S

1

3

2

S

1

3

1

G

3

0

S

1

3

0

S

129

G29

S

12

8

S

127

G2

8

S

126

S

125

G27

S

124

S

12

3

G26

S

122

S

121

G25

S

120

S

119

G24

S

11

8

S

117

G2

3

S

116

S

115

G22

G

3

7

P2

P1

S

74

S

7

3

S

72

S

71

S

70

S

69

G

3

6

S

6

8

S

67

G

3

5

S

66

S

65

G

3

4

S

64

S

6

3

G

33

S

62

S

61

G

3

2

S

60

S

59

G

3

1

S

5

8

S

57

G

3

0

S

56

S

55

G29

S

54

S

5

3

G2

8

S

52

S

51

G27

S

50

S

49

G26

S

4

8

S

47

G25

S

46

S

45

G24

S

44

S

4

3

G2

3

S

42

S

41

G22

G

3

7

+12V

+

3

.

3

V

S

DA

TB_Power_Good

Vcco

Veeprom

TDC_A

ss

ert_CLK_n

TDC_A

ss

ert_CLK

GND

GPIO_24_n

GPIO_24

GND

GPIO_25_n

GPIO_25

GND

GPIO_CC_26_n

GPIO_CC_26

GND

GPIO_27_n

GPIO_27

GND

GPIO_2

8

_n

GPIO_2

8

GND

GPIO_29_n

GPIO_29

GND

GPIO_

3

0_n

GPIO_

3

0

GND

GPIO_

3

1_n

GPIO_

3

1

GND

GPIO_

3

2_n

GPIO_

3

2

GND

GPIO_

33

_n

GPIO_

33

GND

GPIO_

3

4_n

GPIO_

3

4

GND

GPIO_

3

5_n

GPIO_

3

5

GND

GPIO_

3

6_n

GPIO_

3

6

GND

GPIO_

3

7_n

GPIO_

3

7

GND

GND

PCB

Secondary Side

B

a

nk 0

PCB

Primary Side

GND

GPIO_CC_14_n

GPIO_CC_14

GND

GPIO_15_n

GPIO_15

GND

GPIO_16_n

GPIO_16

GND

GPIO_17_n

GPIO_17

GND

GPIO_1

8

_n

GPIO_1

8

GND

GPIO_19_n

GPIO_19

GND

GPIO_20_n

GPIO_20

GND

GPIO_21_n

GPIO_21

GND

GPIO_22_n

GPIO_22

GND

GPIO_2

3

_n

GPIO_2

3

GND

GPIO_5

8

_n

GPIO_5

8

GND

GPIO_59_n

GPIO_59

GND

GPIO_CC_60_n

GPIO_CC_60

GND

GPIO_61_n

GPIO_61

GND

GPIO_62_n

GPIO_62

GND

GPIO_6

3

_n

GPIO_6

3

GND

GND

GPIO_64_n

GPIO_64

GPIO_65_n

GPIO_65

GND

GPIO_66_n

GPIO_67_n

GPIO_66

GND

GND

GPIO_67

G20

G21

S

114

S

11

3

S

112

S

111

S

110

S

109

G1

8

S

10

8

S

107

G17

S

106

S

105

G16

S

104

S

10

3

G15

S

102

S

101

G14

S

100

S

99

G1

3

S

9

8

S

97

G12

S

96

S

95

G11

S

94

S

9

3

G10

S

92

S

91

G9

S

90

S8

9

G

8

S88

S8

7

G7

S8

6

S8

5

G6

S8

4

S83

G5

S8

2

S8

1

G4

G19

S8

0

S

79

G

3

S

7

8

S

77

G2

S

76

S

75

G1

G20

G21

S

40

S3

9

S38

S3

7

S3

6

S3

5

G1

8

S3

4

S33

G17

S3

2

S3

1

G16

S3

0

S

29

G15

S

2

8

S

27

G14

S

26

S

25

G1

3

S

24

S

2

3

G12

S

22

S

21

G11

S

20

S

19

G10

S

1

8

S

17

G9

S

16

S

15

G

8

S

14

S

1

3

G7

S

12

S

11

G6

S

10

S

9

G5

S8

S

7

G4

G19

S

6

S

5

G

3

S

4

S3

G2

S

2

S

1

G1

GND

GND

GPIO_CC_

38

_n

GPIO_CC_

38

GPIO_

3

9_n

GPIO_

3

9

GPIO_40_n

GPIO_40

GND

GPIO_41_n

GPIO_41

GND

GPIO_42_n

GPIO_42

GND

GPIO_4

3

_n

GPIO_4

3

GND

GPIO_44_n

GPIO_44

GND

GPIO_45_n

GPIO_45

GND

GPIO_46_n

GPIO_46

GND

GPIO_47_n

GPIO_47

GND

GPIO_4

8

_n

GPIO_4

8

GND

GPIO_49_n

GPIO_49

GND

GPIO_CC_50_n

GPIO_CC_50

GND

GPIO_51_n

GPIO_51

GND

GPIO_52_n

GPIO_52

GND

GPIO_5

3

_n

GPIO_5

3

GND

GPIO_54_n

GPIO_54

GND

GPIO_55_n

GPIO_55

GND

GPIO_56_n

GPIO_56

GND

GPIO_57_n

GPIO_57

GND

GND

PCB

Secondary Side

B

a

nk 2

B

a

nk 1

B

a

nk

2

B

a

nk 0